| Address | Bits | Name | Type | Default | Description |

| DWORD | BYTE |

| 0x0100 | 0x0400 | REG_CHAN_CNTRL_1 | DAC Channel Control & Status (channel - 0) |

| | | [21:16] | DDS_PHASE_DW[5:0] | R | 0x0000 | The DDS phase data width offers the HDL parameter configuration with the same name. This information is used in conjunction with REG_CHAN_CNTRL_9 and REG_CHAN_CNTRL_10. More info at https://wiki.analog.com/resources/fpga/docs/dds |

| [15:0] | DDS_SCALE_1[15:0] | RW | 0x0000 | The DDS scale for tone 1. Sets the amplitude of the tone. The format is 1.1.14 fixed point (signed, integer, fractional). The DDS in general runs on 16-bits, note that if you do use both channels and set both scale to 0x4000, it is over-range. The final output is (tone_1_fullscale * scale_1) (tone_2_fullscale * scale_2). NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0101 | 0x0404 | REG_CHAN_CNTRL_2 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_1[15:0] | RW | 0x0000 | The DDS phase initialization for tone 1. Sets the initial phase offset of the tone. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

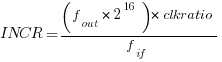

| [15:0] | DDS_INCR_1[15:0] | RW | 0x0000 | Sets the frequency of the phase accumulator. Its value can be calculated by  ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 1 is extended in REG_CHAN_CNTRL_9. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 1 is extended in REG_CHAN_CNTRL_9. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0102 | 0x0408 | REG_CHAN_CNTRL_3 | DAC Channel Control & Status (channel - 0) |

| | | [15:0] | DDS_SCALE_2[15:0] | RW | 0x0000 | The DDS scale for tone 2. Sets the amplitude of the tone. The format is 1.1.14 fixed point (signed, integer, fractional). The DDS in general runs on 16-bits, note that if you do use both channels and set both scale to 0x4000, it is over-range. The final output is (tone_1_fullscale * scale_1) + (tone_2_fullscale * scale_2). NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0103 | 0x040c | REG_CHAN_CNTRL_4 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_2[15:0] | RW | 0x0000 | The DDS phase initialization for tone 2. Sets the initial phase offset of the tone. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase init for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

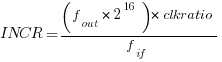

| [15:0] | DDS_INCR_2[15:0] | RW | 0x0000 | Sets the frequency of the phase accumulator. Its value can be calculated by  ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0104 | 0x0410 | REG_CHAN_CNTRL_5 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_PATT_2[15:0] | RW | 0x0000 | The DDS data pattern for this channel. |

| [15:0] | DDS_PATT_1[15:0] | RW | 0x0000 | The DDS data pattern for this channel. |

| 0x0105 | 0x0414 | REG_CHAN_CNTRL_6 | DAC Channel Control & Status (channel - 0) |

| | | [2] | IQCOR_ENB | RW | 0x0 | if set, enables IQ correction. NOT-APPLICABLE if DAC_DP_DISABLE is set (0x1). |

| [1] | DAC_LB_OWR | RW | 0x0 | If set, forces DAC_DDS_SEL to 0x8, loopback If DAC_LB_OWR and DAC_PN_OWR are both set, they are ignored |

| [0] | DAC_PN_OWR | RW | 0x0 | IF set, forces DAC_DDS_SEL to 0x09, device specific pnX If DAC_LB_OWR and DAC_PN_OWR are both set, they are ignored |

| 0x0106 | 0x0418 | REG_CHAN_CNTRL_7 | DAC Channel Control & Status (channel - 0) |

| | | [3:0] | DAC_DDS_SEL[3:0] | RW | 0x00 | Select internal data sources (available only if the DAC supports it).

- 0x00: internal tone (DDS)

- 0x01: pattern (SED)

- 0x02: input data (DMA)

- 0x03: 0x00

- 0x04: inverted pn7

- 0x05: inverted pn15

- 0x06: pn7 (standard O.150)

- 0x07: pn15 (standard O.150)

- 0x08: loopback data (ADC)

- 0x09: pnX (Device specific e.g. ad9361)

- 0x0A: Nibble ramp (Device specific e.g. adrv9001)

- 0x0B: 16 bit ramp (Device specific e.g. adrv9001)

|

| 0x0107 | 0x041c | REG_CHAN_CNTRL_8 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | IQCOR_COEFF_1[15:0] | RW | 0x0000 | IQ correction (if equipped) coefficient. If scale & offset is implemented, this is the scale value and the format is 1.1.14 (sign, integer and fractional bits). If matrix multiplication is used, this is the channel I coefficient and the format is 1.1.14 (sign, integer and fractional bits). NOT-APPLICABLE if IQCORRECTION_DISABLE is set (0x1). |

| [15:0] | IQCOR_COEFF_2[15:0] | RW | 0x0000 | IQ correction (if equipped) coefficient. If scale & offset is implemented, this is the offset value and the format is 2's complement. If matrix multiplication is used, this is the channel Q coefficient and the format is 1.1.14 (sign, integer and fractional bits). NOT-APPLICABLE if IQCORRECTION_DISABLE is set (0x1). |

| 0x0108 | 0x0420 | REG_USR_CNTRL_3 | DAC Channel Control & Status (channel - 0) |

| | | [25] | USR_DATATYPE_BE | RW | 0x0 | The user data type format- if set, indicates big endian (default is little endian). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [24] | USR_DATATYPE_SIGNED | RW | 0x0 | The user data type format- if set, indicates signed (2's complement) data (default is unsigned). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [23:16] | USR_DATATYPE_SHIFT[7:0] | RW | 0x00 | The user data type format- the amount of right shift for actual samples within the total number of bits. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [15:8] | USR_DATATYPE_TOTAL_BITS[7:0] | RW | 0x00 | The user data type format- number of total bits used for a sample. The total number of bits must be an integer multiple of 8 (byte aligned). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [7:0] | USR_DATATYPE_BITS[7:0] | RW | 0x00 | The user data type format- number of bits in a sample. This indicates the actual sample data bits. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| 0x0109 | 0x0424 | REG_USR_CNTRL_4 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | USR_INTERPOLATION_M[15:0] | RW | 0x0000 | This holds the user interpolation M value of the channel that is currently being selected on the multiplexer above. The total interpolation factor is of the form M/N. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [15:0] | USR_INTERPOLATION_N[15:0] | RW | 0x0000 | This holds the user interpolation N value of the channel that is currently being selected on the multiplexer above. The total interpolation factor is of the form M/N. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| 0x010A | 0x0428 | REG_USR_CNTRL_5 | DAC Channel Control & Status (channel - 0) |

| | | [0] | DAC_IQ_MODE[0] | RW | 0x0 | Enable complex mode. In this mode the driven data to the DAC must be a sequence of I and Q sample pairs. |

| [1] | DAC_IQ_SWAP[1] | RW | 0x0 | Allows IQ swapping in complex mode. Only takes effect if complex mode is enabled. |

| 0x010B | 0x042c | REG_CHAN_CNTRL_9 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_1_EXTENDED[15:0] | RW | 0x0000 | The extended DDS phase initialization for tone 1. Sets the initial phase offset of the tone. The extended init(phase) value should be calculated according to DDS_PHASE_DW value from REG_CHAN_CNTRL_1 NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

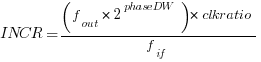

| [15:0] | DDS_INCR_1_EXTENDED[15:0] | RW | 0x0000 | Sets the frequency of tone 1's phase accumulator. Its value can be calculated by  ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_1 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_1 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x010C | 0x0430 | REG_CHAN_CNTRL_10 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_2_EXTENDED[15:0] | RW | 0x0000 | The extended DDS phase initialization for tone 2. Sets the initial phase offset of the tone. The extended init(phase) value should be calculated according to DDS_PHASE_DW value from REG_CHAN_CNTRL_2 NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

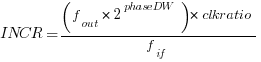

| [15:0] | DDS_INCR_2_EXTENDED[15:0] | RW | 0x0000 | Sets the frequency of tone 2's phase accumulator. Its value can be calculated by  ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_2 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_2 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0110 | 0x0440 | REG_* | Channel 1, similar to registers 0x100 to 0x10f. |

| 0x0120 | 0x0480 | REG_* | Channel 2, similar to registers 0x100 to 0x10f. |

| 0x01F0 | 0x07c0 | REG_* | Channel 15, similar to registers 0x100 to 0x10f. |

| Fri Sep 8 16:01:53 2023 | |