This version (29 Feb 2024 19:47) was approved by Paul Blanchard.The Previously approved version (13 Feb 2024 17:42) is available.

This version (29 Feb 2024 19:47) was approved by Paul Blanchard.The Previously approved version (13 Feb 2024 17:42) is available.

This is an old revision of the document!

CN0584 (Low Latency Development Kit) is a development platform consisting of two boards the EVAL-CN0585-FMCZ and the EVAL-CN0584-EBZ. EVAL-CN0585-FMCZ consists of 4 x 16-bit ADC channels and 4 x 16-bit DAC channels that are interfaced with an FPGA through the FMC Low Pin Count (LPC) Connector. Current revision of EVAL-CN0585-FMCZ is Rev B. EVAL-CN0584-EBZ is the application specific analog front end (AFE) board.CN0584 is connected to a Zedboard to build a development system setup like shown in Figure 7.

The Low Latency Development Kit (LLDK) provides a complete data acquisition and signal generation platform with on-board power rails, voltage monitoring, logic level translation, general purpose I/O, I2C, SPI, and a personality interface connector.

The key performance benefit of the LLDK system is the ability to perform a complete capture and conversion of precision analog input data in <70ns with the ADC module and generate a settled full-scale analog output in <200ns from initial data written to the DAC.

There are four channels of differential input signals on EVAL-CN0584-EBZ.

| Channel | Positive Input Signal | Negative Input Signal |

|---|---|---|

| Channel 0 | J1 | J2 |

| Channel 1 | J3 | J4 |

| Channel 2 | J5 | J6 |

| Channel 3 | J7 | J8 |

Table 1. ADC Input Signal Connectors

LLDK has configurable input voltage ranges of ±10 V(Default), ±5 V, ±4.096 V, ±2.5 V, and ±1.5 V. The input range can be changed by modifying resistor placements on EVAL-CN0584-EBZ as described in Table 2.

| Channel | Input Voltage Range | AFE Board Modification |

|---|---|---|

| Channel 0 | ±10 V (default) | Include R19A, R21A, R22A, R24A; DNI R18A, R20A, R23A, R25A |

| ±5 V | Include R18A, R20A, R23A, R25A; DNI R19A, R21A, R22A, R24A | |

| ±4.096 V | Include R19A, R21A; DNI R18A, R20A, R22A, R23A, R24A, R25A | |

| ±2.5 V | Include R18A, R20A; DNI R19A, R21A, R22A, R23A, R24A, R25A | |

| ±1.5 V | Include R18A, R19A, R20A, R21A; DNI R22A, R23A, R24A, R25A | |

| Channel 1 | ±10 V (default) | Include R19B, R21B, R22B, R24B; DNI R18B, R20B, R23B, R25B |

| ±5 V | Include R18B, R20B, R23B, R25B; DNI R19B, R21B, R22B, R24B | |

| ±4.096 V | Include R19B, R21B; DNI R18B, R20B, R22B, R23B, R24B, R25B | |

| ±2.5 V | Include R18B, R20B; DNI R19B, R21B, R22B, R23B, R24B, R25B | |

| ±1.5 V | Include R18B, R19B, R20B, R21B; DNI R22B, R23B, R24B, R25B | |

| Channel 2 | ±10 V (default) | Include R19C, R21C, R22C, R24C; DNI R18C, R20C, R23C, R25C |

| ±5 V | Include R18C, R20C, R23C, R25C; DNI R19C, R21C, R22C, R24C | |

| ±4.096 V | Include R19C, R21C; DNI R18C, R20C, R22C, R23C, R24C, R25C | |

| ±2.5 V | Include R18C, R20C; DNI R19C, R21C, R22C, R23C, R24C, R25C | |

| ±1.5 V | Include R18C, R19C, R20C, R21C; DNI R22C, R23C, R24C, R25C | |

| Channel 3 | ±10 V (default) | Include R19D, R21D, R22D, R24D; DNI R18D, R20D, R23D, R25D |

| ±5 V | Include R18D, R20D, R23D, R25D; DNI R19D, R21D, R22D, R24D | |

| ±4.096 V | Include R19D, R21D; DNI R18D, R20D, R22D, R23D, R24D, R25D | |

| ±2.5 V | Include R18D, R20D; DNI R19D, R21D, R22D, R23D, R24D, R25D | |

| ±1.5 V | Include R18D, R19D, R20D, R21D; DNI R22D, R23D, R24D, R25D |

Table 2. ADC Input Voltage Range Selection by Resistor Connections

LLDK can support multiple output voltage ranges which can be configured, such as 0 to 2.5 V, 0 V to 5 V, −5 V to +5 V, and −10 V to +10 V, and custom intermediate ranges with full 16-bit resolution. In order to change the output range, resistor placements on the AFE board must be modified and register settings must be applied to AD3552R on EVAL-CN0585-FMCZ as described in Table 4.

| Channel | Output Signal |

|---|---|

| A | J9 |

| B | J10 |

| C | J11 |

| D | J12 |

Table 3. DAC Output Signal Connectors

| Channel | Output Span | VZS (V) | VFS (V) | AFE Board Modification | Register Setting |

|---|---|---|---|---|---|

| CH0 | +/- 10V (Default) | -10.382 | 10.380 | Include R9; DNI R10, R11 | CH0_CH1_OUTPUT_RANGE = 0x100 |

| +/- 5V | -5.165 | 5.166 | Include R11; DNI R9, R10 | CH0_CH1_OUTPUT_RANGE = 0x011 | |

| 10V | -0.165 | 10.163 | Include R11; DNI R9, R10 | CH0_CH1_OUTPUT_RANGE = 0x010 | |

| 5V | -0.078 | 5.077 | Include R10; DNI R9, R11 | CH0_CH1_OUTPUT_RANGE = 0x001 | |

| 2.5V | -0.198 | 2.701 | Include R10; DNI R9, R11 | CH0_CH1_OUTPUT_RANGE = 0x000 | |

| CH1 | +/- 10V (Default) | -10.382 | 10.380 | Include R12; DNI R13, R14 | CH0_CH1_OUTPUT_RANGE = 0x100 |

| +/- 5V | -5.165 | 5.166 | Include R13; DNI R12, R14 | CH0_CH1_OUTPUT_RANGE = 0x011 | |

| 10V | -0.165 | 10.163 | Include R13; DNI R12, R14 | CH0_CH1_OUTPUT_RANGE = 0x010 | |

| 5V | -0.078 | 5.077 | Include R14; DNI R12, R13 | CH0_CH1_OUTPUT_RANGE = 0x001 | |

| 2.5V | -0.198 | 2.701 | Include R14; DNI R12, R13 | CH0_CH1_OUTPUT_RANGE = 0x000 | |

| CH2 | +/- 10V (Default) | -10.382 | 10.380 | Include R15; DNI R16, R17 | CH2_CH3_OUTPUT_RANGE = 0x100 |

| +/- 5V | -5.165 | 5.166 | Include R16; DNI R15, R17 | CH2_CH3_OUTPUT_RANGE = 0x011 | |

| 10V | -0.165 | 10.163 | Include R16; DNI R15, R17 | CH2_CH3_OUTPUT_RANGE = 0x010 | |

| 5V | -0.078 | 5.077 | Include R17; DNI R15, R16 | CH2_CH3_OUTPUT_RANGE = 0x001 | |

| 2.5V | -0.198 | 2.701 | Include R17; DNI R15, R16 | CH2_CH3_OUTPUT_RANGE = 0x000 | |

| CH3 | +/- 10V (Default) | -10.382 | 10.380 | Include R18; DNI R19, R20 | CH2_CH3_OUTPUT_RANGE = 0x100 |

| +/- 5V | -5.165 | 5.166 | Include R19; DNI R18, R20 | CH2_CH3_OUTPUT_RANGE = 0x011 | |

| 10V | -0.165 | 10.163 | Include R19; DNI R18, R20 | CH2_CH3_OUTPUT_RANGE = 0x010 | |

| 5V | -0.078 | 5.077 | Include R20; DNI R18, R19 | CH2_CH3_OUTPUT_RANGE = 0x001 | |

| 2.5V | -0.198 | 2.701 | Include R20; DNI R18, R19 | CH2_CH3_OUTPUT_RANGE = 0x000 |

Table 4. DAC Output Voltage Range Selection by Resistor Connections and Register Settings

The default ADC reference configuration uses the internal 2.048 V, ±0.1% accurate, 20 ppm/°C max voltage reference. For more stringent use cases where the accuracy and temperature drift is an issue, an external LTC6655 2.048 V, ±0.025% accurate, 2 ppm/°C max voltage reference can be used.

The default DAC reference configuration uses the internal 2.5 V, ±0.3% accurate, 10 ppm/°C max voltage reference. For more stringent use cases where the accuracy and temperature drift is an issue, an external ADR4525 2.5 V, ±0.02% accurate, 2 ppm/°C max voltage reference can be used.

| VREF | Jumper Settings |

|---|---|

| ADC_VREF | Short P5 |

| DAC_VREF | Short P4 |

Table 5. Voltage Reference Settings

All power for CN0584 is provided by EVAL-CN0585-FMCZ through the AFE connector. CN0584 uses the +15 V and -15 V rails to provide the positive and negative supply voltages for the ADG5421F input protection switches. The +12 V and -12 V rails provide the positive and negative supply voltages for the ADA4898-1 ADC buffer amplifiers. The +3.3 V rail powers the EEPROM circuit. Power tree information can be found in EVAL-CN0585-FMCZ. Table 6 provides more details on LLDK power rails:

| Power Rail | Description |

|---|---|

| +12 V | LT3045-1 provides the 12V rail supplying up 280mA |

| -12 V | LT3094 provides the -12V rail supplying up to -280mA |

| +15 V | LTM8049 provides the +15V rail at 80% efficiency |

| -15 V | LTM8049 provides the -15V rail at 80% efficiency |

| +3.3 V | Fed through from the FPGA FMC connector to the AFE connector |

Table 6. Power Rail Descriptions

CN0584 is fully supported using a ZedBoard.

Figure 4. EVAL-CN0585-FMCZ revA connected to EVAL-CN0584-EBZ

Figure 5. EVAL-CN0585-FMCZ revB

Figure 5. EVAL-CN0585-FMCZ revB

The following is a list of items needed for system setup:

The box includes a pre-programmed SD card. You can skip the steps in this section and go to the Setting up the Hardware section if using this provided card.

To boot the ZedBoard and control the EVAL-CN0585-FMCZ, you will need to install ADI Kuiper Linux on an SD card. Complete instructions, including where to download the SD card image, how to write it to the SD card, and how to configure the system are provided on the Kuiper Linux page.

Follow the configuration procedure under Configuring the SD Card for FPGA Projects on the Kuiper Linux page. Copy the following files onto the boot directory to configure the SD card (download link for EVAL-CN0585-FMCZ Rev-B sd_card_config_files_revb.zip, for EVAL-CN0585-FMCZ Rev-A sdcard_config_files.zip):

You will need to:

All the products described on this page include ESD (electrostatic discharge) sensitive devices. Electrostatic charges as high as 4000V readily accumulate on the human body or test equipment and can discharge without detection.

All the products described on this page include ESD (electrostatic discharge) sensitive devices. Electrostatic charges as high as 4000V readily accumulate on the human body or test equipment and can discharge without detection.

Although the boards feature ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. This includes removing static charge on external equipment, cables, or antennas before connecting to the device.

The CN0584 can be interfaced with using IIO Oscilloscope, Python, or MATLAB to enable device configuration, capture of incoming samples from the ADCs, and generation of waveforms to be transmitted by the DACs.

Libiio is a library used for interfacing with IIO devices and must be installed on your computer to interface with the hardware.

Download and Install the latest Libiio package on your machine.

To connect to your device, the IIO Osciloscope software must be able to create a context. The context creation in the software depends on the backend used to connect to the device as well as the platform where the EVAL-CN0585-FMCZ is attached. The ZedBoard running ADI Kuiper Linux is currently the only platform supported for the CN0585.

The user needs to supply a URI (Uniform Resource Identifier) which will be used in the context creation. To get the URI, use the command iio_info in the terminal. The iio_info command is a part of the libIIO package that reports all IIO attributes.Upon installation, simply enter the command on the terminal command line to access it.

iio_info

iio_info -u ip:<ip address of your ip>

Example:

IIO Oscilloscope is a cross platform GUI application which can interface with different evaluation boards from within a Linux system.

1- Once done with the installation or an update of the latest IIO-Oscilloscope, open the application. The user needs to supply a URI which will be used in the context creation of the IIO Oscilloscope. If there's only one platform is connected, the IIO Oscilloscope will find URI automatically; If more than one platforms are connected, the user needs to supply the specific URI. The instructions to obtain the URI can be found in the previous section. Note: the “Serial Context” connection method is not enabled.

2- Press refresh to display available IIO Devices and press connect.

Figure 9. IIO Oscilloscope Connection

3- After the board is connected, select the one-bit-adc-dac-device, which is the controller for the MAX7301ATL+ I/O Expander. Then configure pins values of output voltages 0 through 9, by setting the raw value to 1 . Press Write to confirm.

Figure 10. MAX7301ATL Output Channels Configuration

Figure 10. MAX7301ATL Output Channels Configuration

| one-bit-adc-dac device channel | Schematic PIN |

|---|---|

| Voltage0 | GPIO0_VIO |

| Voltage1 | GPIO1_VIO |

| Voltage2 | GPIO2_VIO |

| Voltage3 | GPIO3_VIO |

| Voltage4 | GPIO6_VIO |

| Voltage5 | GPIO7_VIO |

| Voltage6 | PAD_ADC0 |

| Voltage7 | PAD_ADC1 |

| Voltage8 | PAD_ADC2 |

| Voltage9 | PAD_ADC3 |

Table 7. Voltage Configuration for GPIO Pins

4- Input sources for AD3552R devices axi-ad3552r-0 and axi-ad3552r-1 can be configured as dma_input, ramp_input or adc_input.

Select the desired input source for both AD3552R devices axi-ad3552r-0 and axi-ad3552r-1 as dma_input.  Figure 11. AD3552R Input Source Selection in IIO Oscilloscope

Figure 11. AD3552R Input Source Selection in IIO Oscilloscope

5- Select the desired output range for both AD3552R devices.  Figure 12. AD3552R Output Range Selection in IIO Oscilloscope

Figure 12. AD3552R Output Range Selection in IIO Oscilloscope

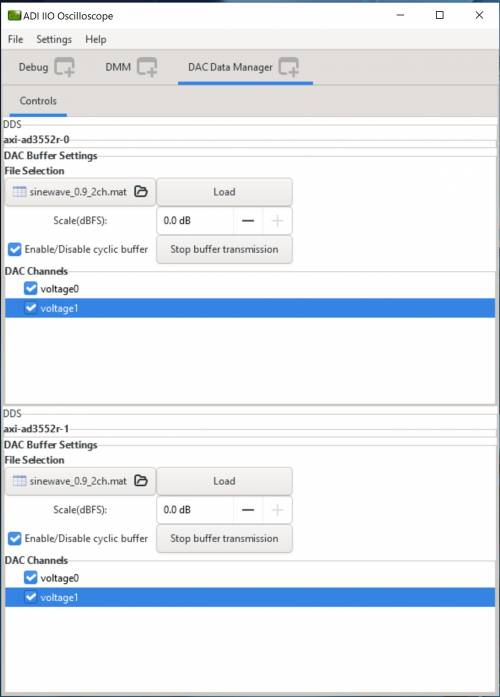

6- From the DAC Data Manager Window select the output channels of the DAC and enable the cyclic buffer for each DAC.

7- Load an example file (.mat, .txt, etc) from the IIO Oscilloscope installation directory, under Program Files/IIO Oscilloscope/lib/osc/waveforms folder.

Figure 13. DAC Data Manager with Example Waves on 4 Channels

Figure 13. DAC Data Manager with Example Waves on 4 Channels

8- Click on the load button.

9- From the Debug window, select the stream_status IIO Attribute and start the stream (start_stream_synced means that all 4 channels are updated at the same time and the data streaming process waits for both DACs to be started).

Figure 14. DAC Stream Status Selection

Figure 14. DAC Stream Status Selection

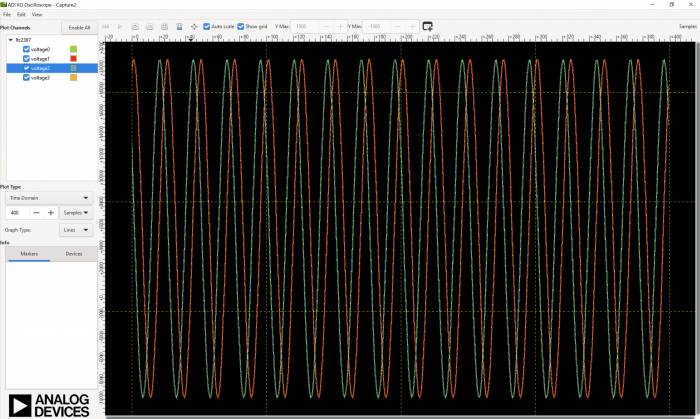

10- After the stream_status has been written and 4 channels are enabled, hit play button. Then data capture window can be seen like in Figure 15.  Figure 15. Captured Loopback Signal

Figure 15. Captured Loopback Signal

The CN0584 can be interfaced to Python using the PyADI-IIO. PyADI-IIO is a Python abstraction module to simplify interaction with IIO drivers on ADI hardware. This module provides device-specific APIs built on top of the current libIIO Python bindings. These interfaces try to match the driver naming as much as possible without the need to understand the complexities of libIIO and IIO.

Follow the step-by-step procedure on how to install, configure, and set up PyADI-IIO and install the necessary packages/modules needed by referring to PyADI-IIO.

Github link for the Python sample script: CN0585 Python Example

After installing and configuring PYADI-IIO on your machine, you are now ready to run Python script examples. To follow this example, run the cn0585_fmcz_example.py found in the examples folder.

D:\pyadi-iio>export PYTHONPATH=D:/pyadi-iio/ D:\pyadi-iio>python examples/cn0585_fmcz_example.py ip:your_board_ip

Press enter and lines below will be observed:

$ python examples/cn0585_fmcz_example.py uri: ip:your_board_ip ############# EEPROM INFORMATION ############ read 256 bytes from /sys/devices/soc0/fpga-axi@0/41620000.i2c/i2c-1/1-0050/eeprom Date of Man : Fri Jan 20 08:11:00 2023 Manufacturer : Analog Devices Product Name : LLDK-LTC2387-AD3552R Serial Number : 56864654 Part Number : 1234 FRU File ID : 12131321 PCB Rev : VB PCB ID : HIL BOM Rev : VC Uses LVDS : Y ############################################# GPIO4_VIO state is: 0 GPIO5_VIO state is: 0 Voltage monitor values: Temperature: 49.25 C Channel 0: 2267.45605283 millivolts Channel 1: 627.4414057359999 millivolts Channel 2: 2061.157224874 millivolts Channel 3: 753.1738275079999 millivolts Channel 4: 2092.285154536 millivolts Channel 5: 2084.960935792 millivolts Channel 6: 2253.4179669039998 millivolts Channel 7: 1809.69238133 millivolts AXI4-Lite 0x108 register value: 0x2 AXI4-Lite 0x10c register value: 0xB Sampling rate is: 15000000 input_source:dac0: dma_input input_source:dac1: dma_input

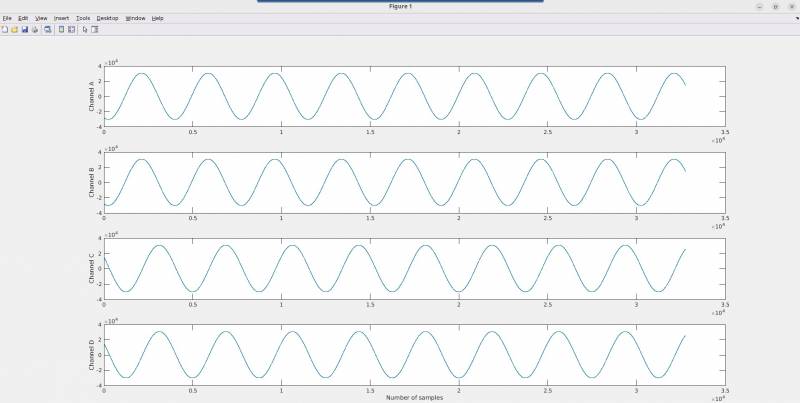

The DAC outputs should be looped back into the ADCs as shown in figure 7 in the System Setup Using a ZedBoard section. After running the script with the board in this configuration, the following window will pop up:

Figure 16: ADC Captured Data Python Plot

Figure 16: ADC Captured Data Python Plot

Required MATLAB Add-Ons:

Github link for the Matlab sample script: CN0585StreamingTest.m

The steps described in the Analog Devices Transceiver Toolbox For MATLAB and Simulink page have to be followed to configure the Matlab/Simulink project using the MathWorks HDL Workflow Advisor.

Remote data streaming to and from hardware is made available through system object interfaces, which are unique for each component or platform. The hardware interfacing system objects provide a class to both configure a given platform and move data back and forth from the device. To run the CN0585StreamingTest.m example, the following steps must be completed first.

1. Ensure MATLAB package “Communications Toolbox Support Package for Analog Devices ADALM-Pluto Radio” is installed from Matlab Add-Ons.

2. Execute the following commands on the computer terminal (Cygwin is recommended for Windows) to set up a local git repository.

git clone https://github.com/analogdevicesinc/HighSpeedConverterToolbox.git cd HighSpeedConverterToolbox git submodule update --init --recursive git checkout cn0585_v1

3. Open Matlab from the HighSpeedConverterToolbox directory.

4. Open CN0585StreamingTest.m from the test subdirectory, update the board_ip variable to match the Zedboard IP address, and finally run the script.

The DAC outputs should be looped back into the ADCs as shown in figure 6 in the System Setup Using a ZedBoard section. After running the script with the board in this configuration, the window in Figure 17 will pop up. :

Figure 17. ADC Captured Data Matlab Plot

Figure 17. ADC Captured Data Matlab Plot

Note the y-axis is plotted in units of ADC codes, and can be converted to voltage by referencing the transfer function on the ADAQ23876 datasheet.

The ZedBoard that drives CN0585 is configured with a HDL reference design which is an embedded system built around a processor core either ARM, NIOS-II, or Microblaze.

Figure 18. HDL Block Design with Simulink HDL_DUT in Rx Configuration

Figure 19. HDL Block Design with Simulink HDL_DUT in Tx Configuration

Figure 20. HDL Block Design with Simulink HDL_DUT in Rx-Tx Configuration

The device digital interface is handled by specific device cores axi_ad35552r for the DAC path and axi_ltc2387 for the ADC path. The cores are programmable through an AXI-lite interface. Details of reference design can be found in Reference Design. HighSpeedConverterToolbox repository supports IP Core generation flow from MathWorks which allows for automated integration of HDL_DUT into HDL reference designs from Analog Devices. The workflow for generating HDL_DUT codes takes Simulink subsystems, runs HDL-Coder to generate source Verilog, and then integrates that into a larger reference design. HDL_DUT can be integrated inside HDL reference design in three different configurations which are Rx,Tx and Rx-TX. Figure 19 and Figure 20 demonstrates how HDL_DUT is placed between Tx and Rx path for these three configuration types. HDL_DUT Code Generation Workflow is described in configuring-matlab

EVAL-CN0584-EBZ Design & Integration Files