This version (18 Aug 2021 14:46) was approved by Laszlo Nagy.The Previously approved version (14 Jan 2021 05:24) is available.

This version (18 Aug 2021 14:46) was approved by Laszlo Nagy.The Previously approved version (14 Jan 2021 05:24) is available.

This is an old revision of the document!

This reference design is not tested in hardware but in testbench, it should serve as a reference for building systems with multiple channels e.g 128 ADC channels and 128 DAC channels or more realized with AD9081 parts.

Reference design location:

Built on top of VCU128 but does not match any FMC connector due the high number of lanes. The design requires 64 lanes for Rx and 64 lanes for Tx, but the FMC+ connector can expose only 24 pairs instead of 64.

Software support for other MxFE projects:

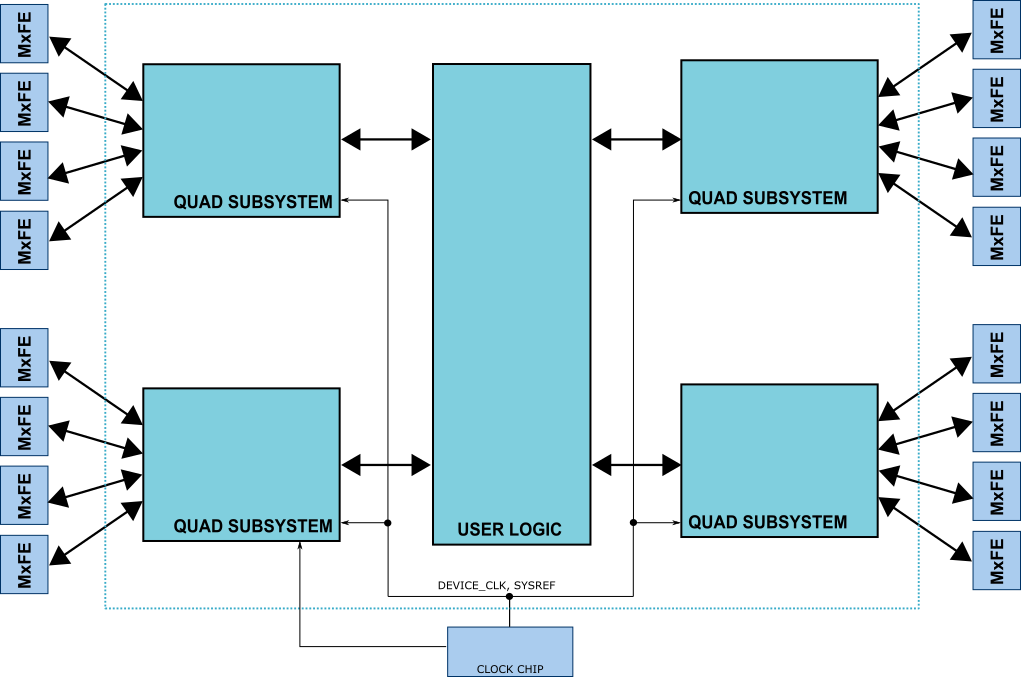

The block design consists of four 'quad jesd subsystem' block components, where each quad block services four Rx/Tx link pairs. Each link pair connects to an AD9081 MxFE chip, where each MxFE chip has 8 ADC and 8 DAC channels. In turn a quad block services a total of 32 ADC and 32 DAC channels.

Having four quad MxFE blocks in parallel gives us 128 ADC and 128 DAC real channels at the transport layer, or 64 complex ADC channels and 64 complex DAC channels.

All quad blocks share a common device clock and SYSREF signal to ensure that samples are aligned at application layer across all channel.

Each quad block contains all components required to handle the JESD link from physical layer to transport layer. The block exposes at its interface raw sample channel streams the user logic can be connected to. The format of the channels is one sample per channel per clock cycle.

A smart interconnect block is added to distribute the control interface to all JESD peripherals. This would lead to better partitioning of the overall design helping the routability and timing closure.

For each quad jesd subsystem the Rx link (ADC Path) operate with the following parameters:

For each quad jesd subsystem the Tx link (DAC Path) operate with the following parameters:

The transport layer cores have optional features (e.g DDS) which can be disabled through synthesis parameter that can impact significantly the resource utilization of the subsystem. Below you can observe the impact of the DDS cores on the utilization.

| Device Family | DDS | CLB LUTs | CLB Registers | XCVR Lanes |

|---|---|---|---|---|

| Xilinx Virtex US+ | Yes | 68535 | 86163 | 16 |

| No | 20332 | 29426 | 16 |

Additional pipeline stages can be enabled in the link layer NUM_INPUT_PIPELINE parameter for the link receive peripheral or NUM_OUTPUT_PIPELINE parameter on the link transmit peripheral. This will break the timing arc between the link layer and physical layer and allow a more relaxed placement of the cores.

The reference clock for each transceiver quad is exposed in the top level file. The reference clocks should be connected to all ports. If there is no reference clock connected to a specific quad, the reference clock for the quad above or below should be used. If that’s not available also, the reference clock for the quad +2 (above the one above) or quad -2 (below the one below) should be used. The overall clock tree for the system (single FPGA or multi FPGA) should ensure all reference clocks are derived from the same crystal. Phase is not important for the reference clocks.

Below are quoted few of the most important guidelines from the JESD standard. For more details consult the standard.

Restriction/requirement particular to the current implementation using the JESD framework:

Analog Devices will provide limited online support for anyone using the reference design with Analog Devices components via the EngineerZone.