Designers may find the following additional information valuable when considering a power scheme for the ADRV9361-Z7035 SDR 2×2.

In addition to the voltages supplied to the SOM on the micro headers, the module uses the 5.0V VIN input to regulate a variety of other voltages required by the system, summarized in the following table.

Regulated Voltage Rails

| Schematic Voltage Name | Voltage(V) | Schematic Symbol | Max Output Current (A) |

|---|---|---|---|

| VCCINT-0P95V | 0.95 | U4 | 1.8 |

| VCC-BRAM | 0.95 | U4 | 1.8 |

| VCCPINT | 1.0 | U4 | 1.8 |

| VCC-1P35 | 1.35 | U4 | 1.8 |

| VCCO-DDR | 1.35 | U4 | 1.8 |

| VTT_0P75 | U14 | 2.0 | |

| VTTVREF | 1/2 VCC-1P35 | U14 | 2.0 |

| VCCPCOM-1P8V | 1.8 | U18 | 4.0 |

| VCCO_1P8V | 1.8 | U18 | 4.0 |

| VDD_INTERFACE | 1.8 | U18 | 4.0 |

| VDDA_GPO | 2.5 | U6 | 0.3 |

| VDDA_GPO_PWR | 2.5 | U6 | 0.3 |

| VCC-3P3V | 3.3 | U9 | 0.5 |

| VCC-3P3V - IO | 3.3 | U9 | 0.5 |

| PHY1_VDD_3V3 | 3.3 | U9 | 0.5 |

| PHY2_VDD_3V3 | 3.3 | U9 | 0.5 |

| 1P3_SUPPLY_A | 1.3 | U19 | 1.2 |

| VDDA_TX_LO | 1.3 | U19 | 1.2 |

| VDDA_RX_LO | 1.3 | U19 | 1.2 |

| VDDA_TX_SYNTH | 1.3 | U19 | 1.2 |

| VDDA_RX_SYNTH | 1.3 | U19 | 1.2 |

| 1P3_SUPPLY_B | 1.3 | U20 | 1.2 |

| VDDA_BB | 1.3 | U20 | 1.2 |

| VDDA_DIG | 1.3 | U20 | 1.2 |

| VDDA_RX_TX | 1.3 | U20 | 1.2 |

| 1P3_TX1A | 1.3 | U20 | 1.2 |

| 1P3_TX2A | 1.3 | U20 | 1.2 |

| 1P3_TX1B | 1.3 | U20 | 1.2 |

| 1P3_TX2B | 1.3 | U20 | 1.2 |

Your system requirements may call for alternate timing, sequencing, and/or monitoring of the SOM power supplies. The ADM1166 Super Sequencer firmware may be updated to accommodate these changes. Be advised that a number factors must be considered, including:

An in depth analysis for calculating ADM1166 thresholds is found here.

Designers are strongly encouraged to start with the latest ADM166.txt file (on Github) and make changes using the Analog Devices Super Sequencer Configuration Tool. Consult the Xilinx Zynq datasheet before making any changes.

Important! Consult the Zynq AP SoC and AD9361 datasheets before updating threshold windows for SOM voltage rails. Sequencing changes are strongly discouraged.

Download the latest ADM1166 firmware repository from the GitHub link below. It’s important to either clone or download the zip archive.

https://github.com/analogdevicesinc/PicoZed-SDR.

Once you have made updates to the ADM1166 firmware file using the configuration tool, there are two methods for programming the device.

A simple Linux script executed on Zynq will download the latest ADM1166 firmware and program the ADRV9361.

You will need a networked router with DHCP capability. Follow the instructions at power-and-sequencing. Look for the section “Programming the ADM1166 Power Sequencer – Using Linux or HyperTerminal Program”.

This method clones the Analog Devices GIT repository to obtain the latest version of the HEX file for the ADM1166. Note that you need to login as root or use the ‘sudo’ command to execute the update. The GitHub repository for these files is at the following github.

Alternatively, you may use the Manual Update Procedure.

This is an optional “manual” method to update the ADM1166 firmware, provided if you are unable to connect your development kit to a DHCP networked router.

This method can also be used to program your own custom ADM1166 firmware, however consider whether your custom thresholds will be compatible with the carrier you are using during this process. Upon completion the board may shutdown. The only way to recover from this situation is to use the USB adapter to program the SOM standalone.

The ADM1166 Super Sequencer non-volatile memory can be programmed by connecting an Analog Devices USB-SDP-CABLEZ I2C/SMBus programmer to the SOM 5-pin P1 connector. Supplying 5.0V to VBUS pin P1-1 allows the device to be powered and programmed without mating the SOM to a carrier. Software support for the programmer can be found on the ADM1166 product page.

Important! Damage may occur to the SOM if the ADM1166 sequencing state machine is reprogrammed without regard for the required sequencing of the system. Consult the Zynq-7000 SoC and Analog Devices AD9361 datasheets before modifying the sequencing scheme.

ADM1166 Programming Port (P1)

Instructions for programming: https://wiki.analog.com/resources/eval/user-guides/pzsdr/power-and-sequencing Look for the section titled “Using the USB-SDP-CABLEZ Serial I/O Interface”.

The ADRV9361 2×2 SOM cannot supply USB power. The USB PHY (U15) on the SOM includes a CPEN signal which is brought to a micro header pin for use as an enable for a USB t5V power supply on the carrier card. 7.4 XADC Power Configuration The Zynq SoC’s XADC component is powered from the filtered 1.8V VCCaux supply (VCCPCOM-1P8V) utilizing the on-chip reference as shown below:

During the course of development with the Analog Devices Linux reference design, should your 8 GB SD card become corrupted or otherwise need to be updated, the directions below will restore the system to the latest version. Instructions are provided for both Linux and Windows hosts.

These steps will overwrite the contents of the SD card, so be certain there is no existing data that needs to be retrieved from the SD card prior to following these steps.

Otherwise, you may simply run the update scripts at the command line: https://wiki.analog.com/resources/tools-software/linux-software/zynq_images#staying_up_to_date

As a final step, make sure to copy the contents of the ‘zynq-picozed-sdr2’ folder to the BOOT partition of the SD card. PicoZed SDR is now fully updated and ready to re-boot.

Internal only. None released. Identification – REV A printed in copper.

First hardware shipped to customers. Identification – Sticker printed with RFSOM REV B located on the bottom side just above the copper etch AES-PZSDR-Z7035-AD9361-G.

Small updates. Functionally is equivalent to Rev B (see list of changes below). Identification – Initial builds used a sticker printed with an Sxx-xxxx designator and an enumerated SN:xxxxxxx serial number, but no revision printed. Subsequent builds add a REVC revision text to the label.

Changes from Rev B to Rev C

Moved GTX ports from Bank 111 to Bank 112 on the Zynq SoC, and modified the control for PG_MODULE. Otherwise, functionally is equivalent to Rev B and Rev C (see list of changes below). Identification – Sticker printed with an Sxx-xxxx designator, an enumerated SN:xxxxxxx serial number, board part number, and revision REVD.

Changes from Rev C to Rev D

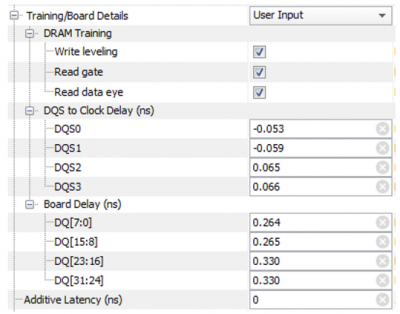

The Xilinx Vivado tools allow entry of the DDR3L trace lengths in order to optimize timing and performance of the PS-based memory controller. The trace lengths for PicoZed SDR 2×2 are listed below. These are also found in the reference design TCL build scripts available on the Analog Devices GitHub repository.

DDR3L Trace Lengths