EVALUATING THE AD9094 ANALOG-TO-DIGITAL CONVERTER

Preface

This user guide describes the AD9094 evaluation board AD9094-1000EBZ which provides all of the support circuitry required to operate the ADC in its various modes and configurations. The application software used to interface with the devices is also described. The user guide wiki applies to the following evaluation boards:

| Evaluation Board Part Number | Description | Board Revision |

| AD9094-1000EBZ | Evaluation board for AD9094-1000 | 9694CE04A |

The AD9094 data sheet provides additional information and should be consulted when using the evaluation board. This guide assumes the usage of the accompanying ADS7-V2EBZ High Speed Evaluation Board. The user guide for the ADS7-V2 provides additional information available for consultation during usage. All documents and software tools are available at www.analog.com/hsadcevalboard.

For additional information or questions, post a question on Engineer Zone, or send an email to highspeed.converters@analog.com.

AD9094 Evaluation Board

Typical Measurement Setup

The AD9094-1000EBZ can be evaluated using the ADS7-V2EBZ FPGA data capture board. The figures below show the AD9094-1000EBZ connected to the ADS7-V2EBZ.

Warning: The AD9094-1000EBZ is electrostatic discharge (ESD) sensitive. Handle the device with care, and employ conducting wrist straps or antistatic bags when handling the board.

Features

Helpful Documents

Software Needed

Design and Integration Files

Equipment Needed

Getting Started

This section provides quick start procedures for using the evaluation board for AD9094.

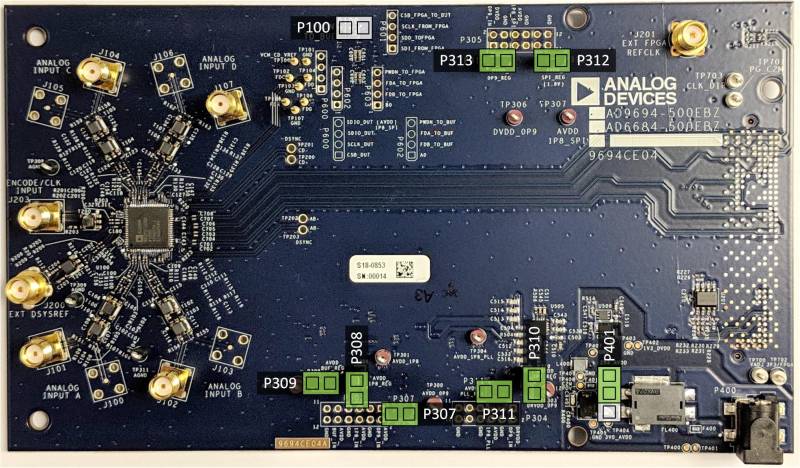

Configuring the Board

Before using the software for testing, configure the evaluation board as follows:

Connect the evaluation board to the

ADS7-V2EBZ data capture board, as shown in the figure for the

Evaluation Board Connection.

Make sure the jumpers are placed on the evaluation board as highlighted in green in the figure AD9094 Evaluation Board.

Ensure that the S1 on ADS7-V2 is off. Connect one 12V, 6.5A switching power supply (such as the CENB1080A1251F01 supplied) to P4 on the

ADS7-V2EBZ board. Connect the Standard-B

USB port of the

ADS7-V2EBZ board to the PC with the supplied

USB cable.

-

-

If the Device Manager does not show the

ADS7-V2EBZ listed, unplug all

USB devices from the PC, uninstall and re-install SPIController and VisualAnalog and restart the hardware setup from step 1.

On the ADC evaluation board, provide a clean, low jitter 1GHz clock source to connector J203 and set the amplitude to 14dBm. This is the ADC Sample Clock.

On the

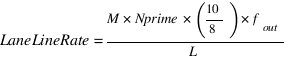

ADS7-V2EBZ data capture board, provide a clean, low jitter clock source to connector J3 and set the amplitude to 10dBm. This is the Reference Clock for the gigabit transceivers in the FPGA. The REFCLK frequency can be calculated using the following empirical formulae:

bps/lane, where

bps/lane, where

(Default Nprime = 16)

(Default Nprime = 16)

On the ADC evaluation board, use a clean signal generator with low phase noise to provide an input signal for channel A to J101. Use a shielded, RG-58, 50 Ω coaxial cable to connect the signal generator output to the ADC Evaluation Board. For best results, use a narrow-band, band-pass filter with 50 Ω terminations and an appropriate center frequency. (

ADI uses TTE, Allen Avionics, and

K & L band-pass filters.) If providing an input clock with a divide-by-1 setting in the AD9094 make sure the clock source has a 50% duty cycle. For optimum SNR performance use the clock divider with a divide ratio of 2 or higher to minimize the impact of the phase noise from the input clock source.

On the ADC evaluation board, use a clean signal generator with low phase noise to provide an input signal for channel B to J102. Use a shielded, RG-58, 50 Ω coaxial cable to connect the signal generator output to the ADC Evaluation Board. For best results, use a narrow-band, band-pass filter with 50 Ω terminations and an appropriate center frequency. (

ADI uses TTE, Allen Avionics, and

K & L band-pass filters.)

On the ADC evaluation board, use a clean signal generator with low phase noise to provide an input signal for channel C to J104. Use a shielded, RG-58, 50 Ω coaxial cable to connect the signal generator output to the ADC Evaluation Board. For best results, use a narrow-band, band-pass filter with 50 Ω terminations and an appropriate center frequency. (

ADI uses TTE, Allen Avionics, and

K & L band-pass filters.)

On the ADC evaluation board, use a clean signal generator with low phase noise to provide an input signal for channel D to J107. Use a shielded, RG-58, 50 Ω coaxial cable to connect the signal generator output to the ADC Evaluation Board. For best results, use a narrow-band, band-pass filter with 50 Ω terminations and an appropriate center frequency. (

ADI uses TTE, Allen Avionics, and

K & L band-pass filters.)

Visual Analog Setup

Click Start

All Programs

Analog Devices

VisualAnalog

VisualAnalog

On the VisualAnalog “New Canvas” window, and select the desired canvas.

Note: The current canvases for VisualAnalog only support operating both pairs of channels in the AD9094 in the same chip operating mode with the same decimation rate. If Pair AB is in full bandwidth mode then Pair CD must also be in full bandwidth mode. If Pair AB is in real DDC0/DDC1 mode with a decimation rate of 2 then pair CD must also be in real DDC0/DDC1 mode with a decimation rate of 2.

Next, program the FPGA in VisualAnalog by clicking into the

ADC Data Capture Settings block and selecting the

Capture Board tab. Use the

Browse button to navigate to the

ad9694_ads7v2.bin file and then click

Program. The

FPGA_DONE LED should illuminate on the ADS7-V2 board indicating that the FPGA has been correctly programmed.

Warning: Programming the FPGA will power the AD9094 evaluation board via the FMC connector. Removing any of the board's power jumpers while the board is on or in operation may cause damage to the board and/or chip. Removing the board while it is being powered via the FMC connector may also cause damage to the board.

Click the

General button in the

ADC Data Capture Settings block. On the

General tab make sure the clock frequency is set at the sample rate. For example, if the input clock to the AD9094 is 1000

MHz then set the

Clock Frequency (MHz) to 1000

MHz. The FFT capture length may be changed to 131072 (128k) or 262144 (256k) per channel. The ADS7-V2 FPGA software supports up to 2M FFT capture (1M per channel).

Changing the ADC Capture Settings

If VisualAnalog opens with a collapsed view, click on the “Expand Display” icon

On the Device tab. Make sure that Enable Alternate REFCLK option is checked.

Click OK

ACE Setup

Click Start

All Programs

Analog Devices

ACE

ACE

Once ACE opens the AD9094 evaluation board should appear in the

Attached Hardware section.

ACE Attached Hardware: AD9094

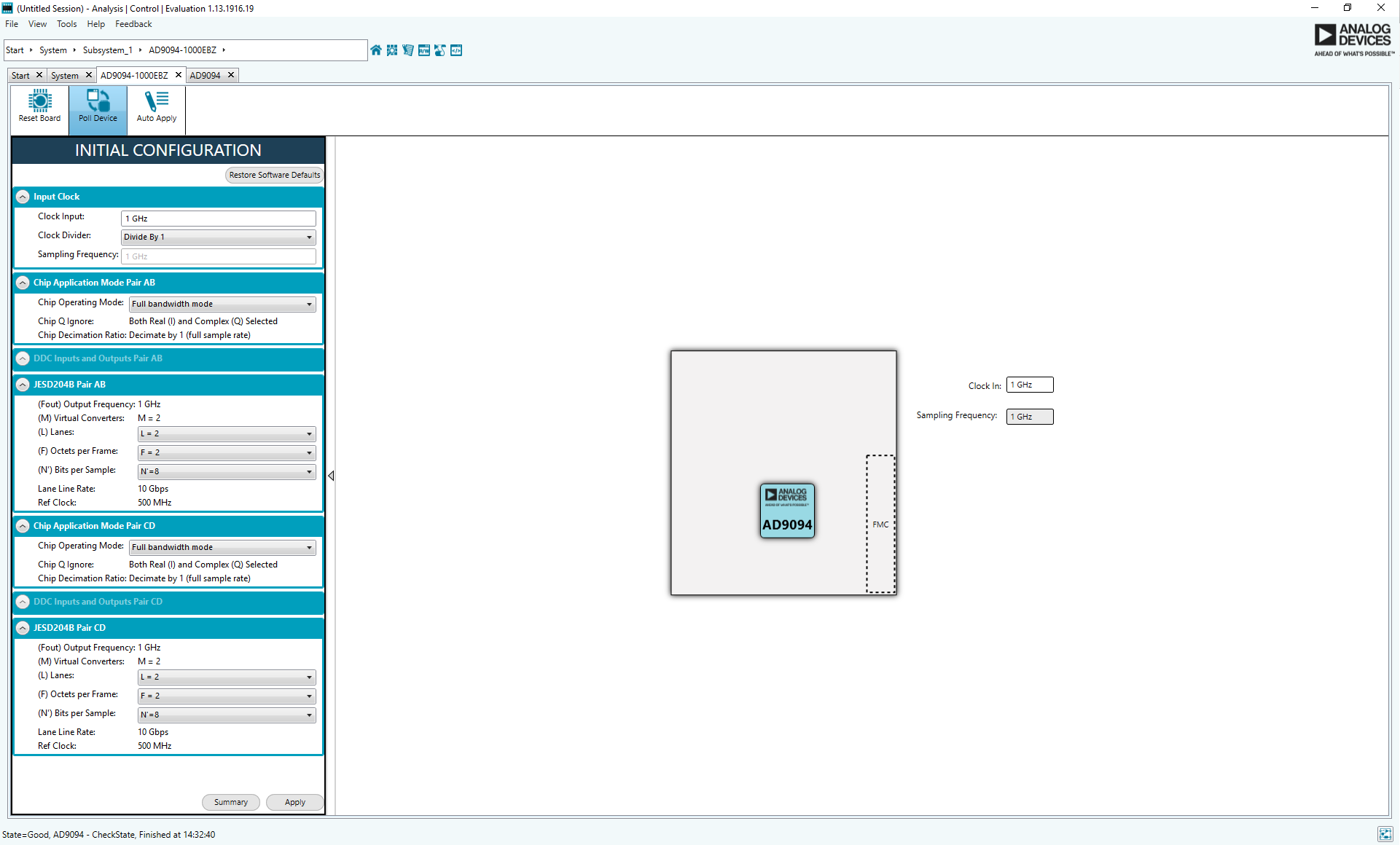

Double click on the

AD9094 Eval Board icon which will open up the Initial Configuration wizard. The default conditions for the AD9094 are Full BW mode with a sample clock of 1

GHz. From here both pairs of ADC channels (Pair AB and Pair CD) can be configured simultaneously.

NOTE:It is important to remember that the AD9094 functions as two dual ADCs.

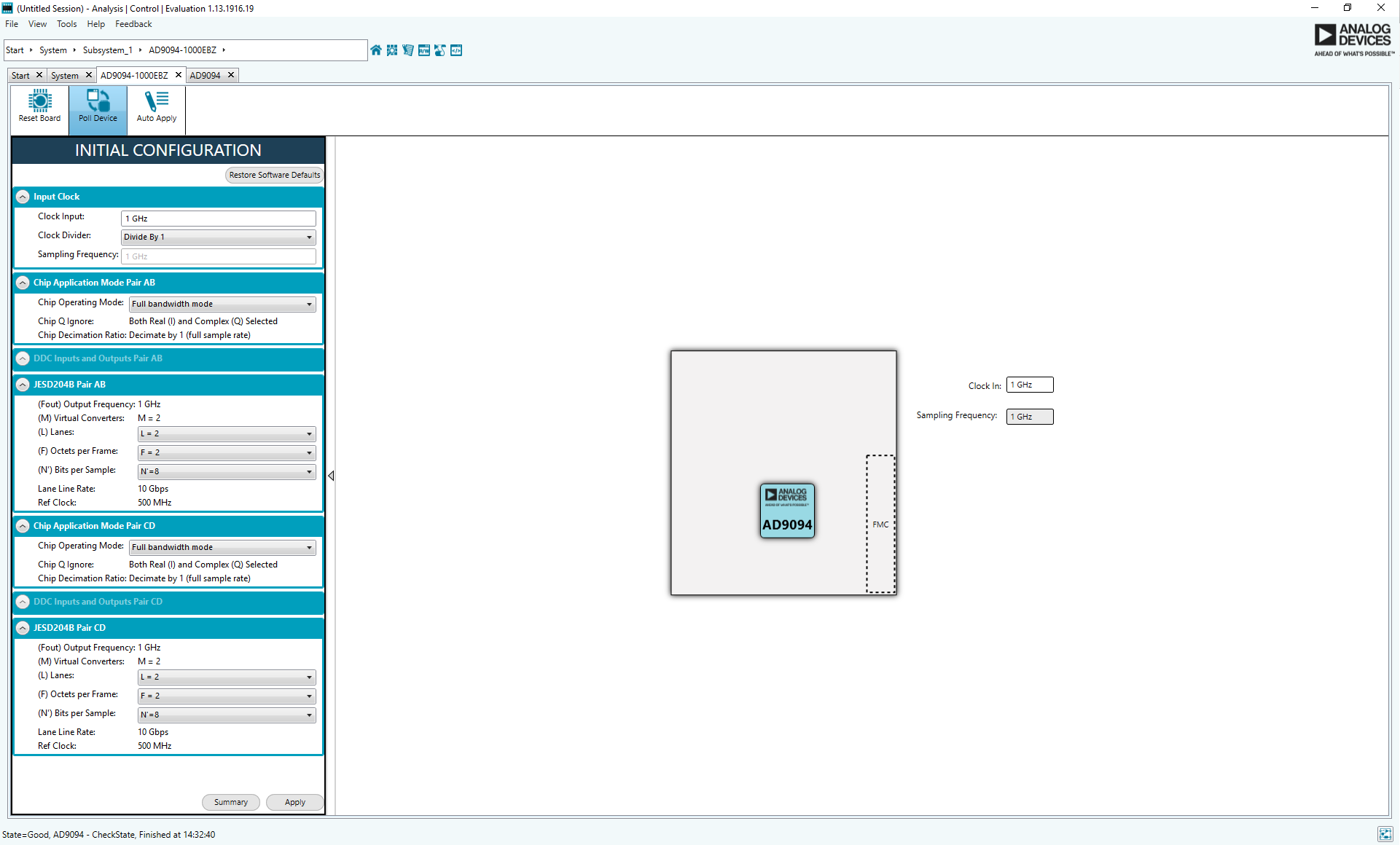

ACE - AD9094 Initial Configuration Wizard

Prior to configuring any modes in the AD9094 double click on the

AD9094 icon to bring up the device view. From the device view click on the

Read All icon to read the

SPI settings from the device. Do this for each pair by selecting one pair at a time and then clicking the

Read All icon.

ACE - AD9094 Initial Configuration Wizard

From the the Initial Configuration Wizard the clock frequency, chip application mode (per pair), DDC inputs and outputs, and the JESD204B settings can be quickly configured. The default conditions are:

-

Clock Divider = Divide by 1

Chip Operating Mode = Full Bandwidth Mode

JESD204B Parameters:

L.M.F = 2.2.2 ;

N' = 8

All these parameters can be seen below:

ACE - AD9094 Initial Configuration Wizard Showing JESD204B Parameters

Device Setup - Full BW Mode

The default Chip Application Mode for the

AD9094-1000EBZ is Full BW mode. In this example the clock frequency will be set to

1000 MHz, the clock divider set to

Divide by 1, and the chip operating mode set to

Full BW Mode. Once the settings have been entered, click

Apply. This will configure the device with the selected settings and provide an

Initial Configuration Summary which will summarize the settings that have been loaded into the AD9094 and also provide the frequency for the required FPGA reference clock.

Default Application Mode - Full BW Mode (click to enlarge)

In order to change the settings for each channel, double-click on the AD9094 icon from the

AD9094 Eval Board view (highlighted in the figure below).

Double-click the AD9094 Icon in the Eval Board View

This will bring up the AD9094 device view showing more specific settings for each pair and channel. The device view shows one pair of the AD9094 at a time. The

ADC Pair Selection drop down box is used to select the current pair. To select the desired pair (Pair AB or Pair CD) select the desired pair from the drop down box. This sets the current changes to affect the select pair only. The settings can now be configured for each channel. Once the settings are configured click

Apply Changes in the upper left of the device view. This will load the setting changes to the selected ADC pair and channel(s). If the settings are desired for all four channels then click the

Apply button in the

AD9094 Configuration window on the left of the screen. This loads the current settings to all channels in the device.

Pair AB - Channel A and Channel B NSR Settings (click to enlarge)

The device view in ACE also has controls for the analog input controls. The input buffer current, input full-scale voltage, and analog input differential termination can be adjusted. The analog inputs can also be disabled from this menu.

Analog Input Control Settings

The

Memory Map View can be accessed from the AD9094

Device View. The

Memory Map View can be used to individually write registers in the AD9094.

Note: When writing individual registers it is imperative to first write the Pair Index register (0x0009) before any other write so that the correct ADC channel pair (Pair AB or Pair CD) is being addressed. If writing a local register, subsequently write the ADC channel index register (0x0008) so that the desired channel within the desired pair is written (Channel A/C or Channel B/D).

Memory Map View (click to enlarge)

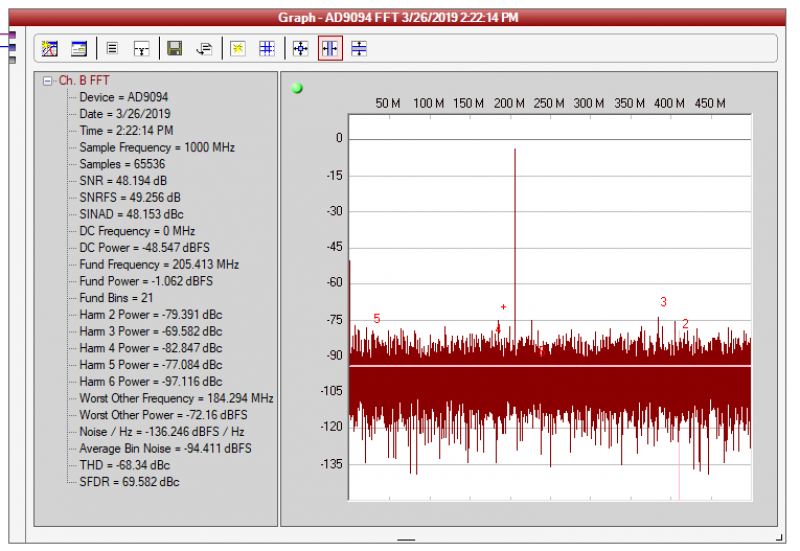

Obtaining an FFT - Full BW Mode

The first item to configure in Visual Analog is the input clock frequency. Click in the ADC Data Capture block to open the settings. In this example, 1000

MHz is the input clock frequency so 1000 is entered into VisualAnalog.

AD9094 FFT Data Capture Settings

In this example, with an input clock of 1000MHz, the output lane rate is 10 Gbit/s. The default JESD204B lane configuration for the JESD204B link of each ADC Channel Pair is 2.2.2 (L.

M.F). The required REFCLK frequency is 500

MHz (refer to step 7 in the section “Configuring the Board”).

Click the Run button in Visual Analog and you should see the capture data similar to the plot below.

AD9094 FFT with NSR Enabled (Tuning Word = 58)

Adjust the amplitude of the input signal so that the fundamental is at the desired level. (Examine the

Fund Power reading in the left panel of the VisualAnalog FFT window.) NSR imposes a ~3dB loss in the signal, but does not impact the dynamic range. A -1.0

dBFS input signal will show as -4.0

dBFS in the FFT in Visual Analog.

To save the FFT plot do the following

Click on the Float Form button in the FFT window

Click on File

Save Form As button and save it to a location of choice

Troubleshooting Tips

EVALUATION BOARD ISN'T FUNCTIONING PROPERLY

It is possible that a board component has been rendered inoperable by

ESD, removing a jumper during powered operation, accidental shorting while probing, etc. Try checking the supply domain voltages of the board while it is powered. They should be as follows:

| Domain | Jumper | Test Point | Approx. Voltage |

| AVDD_0P9 | P307 | TP303 | 0.95 V |

| AVDD_1P8 | P308 | TP304 | 1.80 V |

| AVDD_BUF | P309 | TP305 | 2.50 V |

| DRVDD_0P9 | P304 | TP301 | 0.95 V |

| AVDD_1P8_PLL | P311 | TP306 | 1.80 V |

| DVDD_0P9 | P305 | TP302 | 0.95 V |

| AVDD_1P8_SPI | P312 | TP307 | 1.80 V |

If a short is detected between any of the supply domains and ground, or an open is detected across fuse chip F401 (next to P401), a component may have been damaged. This may have occurred from jumper or board removal while being actively powered (See the warning in the

ACE Setup section). See the

Design Integration Files section for the schematic and/or bill of materials for the relevant components to test and/or replace.

EVALUATION BOARD IS NOT COMMUNICATING WITH THE ADS7-V2 / NO SPI COMMUNICATION

Make sure that the FPGA on the ADS7-V2 has been programmed - a lit LED DS15 (FPGA_DONE) on the top of the ADS7-V2 and a powered fan are good indicators of the FPGA being programmed.

Check the common mode voltage on the JESD204B traces. On the evaluation board, the common mode voltage should be roughly two-thirds of DRVDD_0P9. On the ADS7-V2, the common mode voltage should be around 1.2 volts.

Check Test Point 307 - test point for the AVDD_1P8_

SPI supply domain, jumper P312 - and make sure it is around 1.8 volts.

To test

SPI operation, attempt to both read and write to register 0x000A using ACE's Register Debugger (View → Register Debugger). This register is an open register available for testing memory reads and writes. If the value written to this register does not reset after writing it,

SPI is operational.

All registers reading back as either all ones or all zeros (

i.e., 0xFF or 0x00) may indicate no

SPI communication.

Register 0x0000 (

SPI Configuration A) reading back 0x81 in ACE may indicate no

SPI communication as a result of the FPGA on the ADS7-V2 not being programmed.

EVALUATION BOARD FAILS TO CAPTURE DATA

Ensure that the board is functioning properly and that

SPI communication is successful - see previous troubleshooting tips.

Check the Clock Detect register 0x011B to see if the inputted clock is being detected. 0x01 indicates detection, 0x00 indicates no clock detected. Check the signal generator inputting on connector J203. Try placing a differential oscilloscope probe on the clock pins to see if the clock signal is reaching the chip.

Check the

PLL Locked indicator or register 0x056F (

PLL Status). If the light is green / if the register reads back 0x80, the

PLL is locked. If it is not locked:

Check the clock being inputted to connector J203

Check the JESD settings under the Initial Configuration. Reference the

AD9094 datasheet for supported lane options.

Check the reference clock and make sure it matches your JESD settings.

Make sure P100 (Power Down / Standby Jumper) is not jumped.

bps/lane, where

(Default Nprime = 16)