The easy to use ADALM2000 active learning module (M2K) helps introduce electrical engineering students and hobbyists to the fundamentals of signals and systems. Designed for students at all levels and from all backgrounds, the module can be used for both instructor-led and self-directed learning to help students develop a foundation in exploring signals and systems into the tens of MHz that they can build on as they pursue science, technology, or engineering degrees, without the cost and bulk associated with traditional lab gear.

With 12-bit ADCs(running at 100MSPS) and DACs(at 150MSPS), the ADALM2000 brings the power of high performance lab equipment to the palm of your hand. When coupled with Analog Devices' Scopy graphical application software running on a computer, provides the user with the following high performance instrumentation:

Small enough to fit in a shirt pocket, the M2K is completely self-contained and entirely USB powered with the default firmware. Because M2K is enabled by libiio drivers, it supports OS X® , Windows®, and Linux®, which allows students to learn and explore on a variety of host platforms. In addition, the cross-platform libm2k interface library allows users to communicate with the M2K their own C, C#, or Python programs.

Figure 1. ADALM2000

Figure 2. ADALM2000 Pinout

The ADALM2000 board is based on the Xilinx Zynq All Programmable SoC (AP SoC) which integrates the software programmability of an ARM-based processor with the hardware programmability of an FPGA, enabling hardware acceleration while integrating CPU, DSP, ASSP, and mixed signal functionality into a single device. The device used in the M2K features a single-core ARM Cortex™-A9 processor mated with 28nm Artix®-7 based programmable logic, outfitted with commonly used hardened peripherals (USB, SPI, etc.)

The high-level block diagram of ADALM2000 is presented in Figure 3. The Scopy software application will automatically detect the board and communicate with it via USB 2.0, while the functional blocks of ADALM2000 can be controlled via libm2k interface, including parameters configuration, acquiring, storing and transferring data.

Figure 3. ADALM2000 block diagram

The block diagram is divided in the following blocks:

The AD9963 is a 12-bit, low power Mixed signal Front end converters that provides two ADC channels with sample rates of 100 MSPS and two DAC channels with sample rates to 170 MSPS. The AD9963 offers high performance with low power consumption, high integration and a flexible digital interface. The M2K operates the ADC channels at a maximum sample rate of 100 MSPS, and the DAC channels at a maximum sample rate of 150 MSPS.

Figure 4. AD9963 ADC/DAC

The gain mode is selected in this stage by the SoC, enabling the corresponding switch from ADG612 device. ADG612 is a monolithic CMOS device containing four independently selectable switches with the characteristics:

The ADALM2000 hardware design includes two gain range settings for the analog input voltage divider:

A logic high on EN_SC1_HG turns switch 1 and switch 3 on, selecting high gain mode (gain of ).

A logic high on EN_SC1_LG turns switch 2 and switch 4 on, selecting low gain mode (gain of ).

Where:

Figure 5. Input divider and gain control stage

After the input divider stage in the signal chain is the buffer stage. A dual AD8066 FET input Op Amp is configured as a unity-gain buffer that presents a high-impedance to the dividers' outputs and drives the following stage. R-C compensation networks in the figure help to maximize the bandwidth and reduce peaking (especially at unity gain).

Figure 6. Buffer stage

The useful features of the AD8066 are:

The ADC driver consists of a ADA4940 for each analog input channel. This fully differential ADC driver is a low noise, low distortion device, with very low power consumption. Along with the passive components, this stage gives gain factor equal to 1.3 for the differential signal that comes from the previous buffer stage and a gain factor equal to 1 for the offset and reference signals.

Another ADA4940 and 2 Schottky diodes are used to provide protection to the ADC inputs of each channel against voltage levels above the absolute maximum ratings. In the datasheet of AD9963 the full scale input range of the ADC is 1.56Vpp differential with an absolute maximum rating from -0.3V to 2.1V so the protection circuit will clamp voltages around these values.

Figure 7. ADC Driver

Reference and offset voltages are implemented with an AD8567, a dual, micropower, precision, rail-to-rail input/output amplifier optimized for high output current capability and large capacitive loads. Other features of this operational amplifier are:

The reference stage has a 1.2V reference input signal. The reference signal is amplified with a gain equal to 1.333 before it reaches the ADC driver.

Figure 8. Reference Amplifier

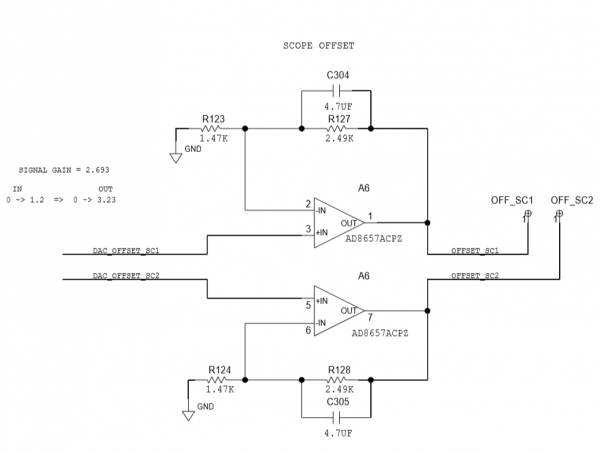

In the offset stage, the input signal is generated by AD5625 12-bit nanoDAC. This signal is amplified with 2.693 before it reaches ADC driver.

Figure 9. Offset Amplifier

The reference and offset voltages are derived from an AD5625 nanoDAC, which uses a 2-wire I2-compatible serial interface.It has single supply operation(from 2.7V to 5.5V) and is guaranteed monotonic by design.

Figure 10 . AD5625 nanoDAC

The AD9963 DACs are a current steering architecture, so it is necessary to convert the TXIP,TXIN,TXQP,TXQN outputs to a voltage for the AWG frontend. This operation is performed by an AD8058 dual voltage feedback amplifier.

The output currents from the TXIP and TXIN pins are complementary, meaning that the sum of the two currents always equals the full-scale current of the DAC. The digital input code to the DAC determines the effective differential current delivered to the load. TXIP provides maximum output current when all bits are high. The output currents vs. DACCODE for the DAC outputs are expressed as

where

The DAC full-scale output current is regulated by the reference control amplifier and is determined by the product of a reference current, a programmable reference resistor, an internal programmable resistor, and a pair of programmable gain scaling parameters. There are a number of adjustments that can be made to scale IOUTFS

to provide programmability in the output signal level.

There are 2 available ranges for the DAC full scale current: 4 mA full scale or 1 mA full scale. This current is converted by the AD8058 into voltage for the last stages of the AWG front end.

Figure 11. Current to voltage converter

The AD8058 has a very low input bias current value (typically 0.5 µA) and is and is configured as a current to voltage converter such that:

The output voltage range of the AD8050 will be different, depending on the DAC full scale output current:

| Input current (AD8058) | Output Voltage (AD8058) |

| 4 mA FS | -0.496 V → 0.496 V |

| 1 mA FS | -0.124 V→ 0.125 V |

The AWG reference is generated with ADR3412 high accuracy voltage reference. The 1.2 V signal is then passed through a buffer implemented with AD8657.

Figure 12. AWG reference

The offset of the signal generator channels is provided by the AD5625 nanoDAC.

Figure 13. Gain and offset stage of the AWG frontend

The ADF4360-9 is the clock generator used in ADALM2000, with a 20MHz reference generated by a precision oscillator(Y1). This integrated integer-N synthesizer and voltage controlled oscillator (VCO) allows a frequency range of between 65 MHz to 400 MHz. The ADF4360-9 is programmed through a 3-wire interface, the power supply range is 3.0 V to 3.6 V, and a low-power shutdown mode reduces supply current to 7μA.

Figure 14. Oscillator and Clock Generator

Figure 15. Digital I/O

Digital IO connections to P1 are shown in the figure above. P1 is the end user signal connector, with 30 pins corresponding to the input analog channels, the user power supplies, the signal generator channels, 4 GND pins and digital IO pins. The Digital IO interface includes 18 pins, 16 of which are the Digital IO channels and the other two are trigger pins. IO pins are LVCMOS3V3 compatible and have ESD protection for large currents provided by Schottky Diodes (D11-D19). Short circuit protection is provided by the PRG18BB221MB1RB PTC protection devices on the digital lines (RT10-18). These components provide fault protection at the expense of limiting the bandwidth of the digital pins slightly when configured as inputs. Similarly, in digital output mode, the 200Ω resistance and the capacitance of the circuit being driven will limit bandwidth.

input bandwidth calculation based on 200Ω and 4.4pF + Zynq Cin

Note: When connecting the digital pins to any external device and the ADALM2000 is powered off, the ESD protection diodes on the ADALM2000 will turn on, pulling any signals to ground. Any high logic level of the external signal will be reduced to ~ 0.6V.

Would be good to describe a practical series resistance to safely sniff 5V logic, considering the unpowered case where the internal 3.3V supply could potentially be “dragged” higher than 3.3V

The user power supplies are implemented with two ADA4805 amplifiers, one in noninverting configuration for the positive power supply and the other in inverting configuration for the negative power supply. These amplifiers are rail-to-rail output, with ultralow pupply current (500µA per amplifier) and with a typical 0.2 µV/°C offset drift. A shutdown pin allows dynamic management of the amplifier's supply current. The outputs are guaranteed to source and sink 58mA, making them suitable for use as an adjustable positive or negative power supply with a maximum specified load current of 50mA. Compensation networks allow the amplifier to drive a 1μF output capacitance, providing a low AC output impedance to the load.

Figure 16. User power supplies

The ADA4805 shutdown pin is controlled by the SoC through a p-Channel MOSFET. The device will turn of if the pin is pulled to a voltage with more than 1V below midsupply.

Figure 17. Enable supplies

Control signals for the supplies are generated by an AD5627 dual 12 bit nanoDAC, with an output range of 0-1V corresponding to a range of 0 to 5.02V for the positive supply and 0 to -5.1V for the negative supply.

Figure 18. AD5627 nanoDAC

The amplifier used for the positive user power supply has a gain of 5.02:

For the negative user supply amplifier the gain is -5.1:

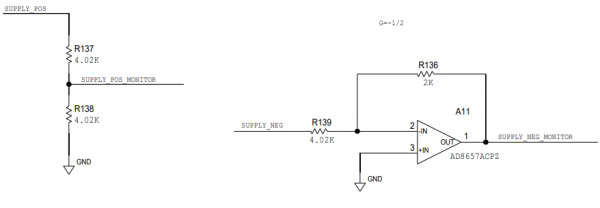

The outputs of the ADA4805s (SUPPLY_POS and SUPPLY_NEG) correspond to the V+ and V- pins on the user connector. Output voltages are also monitored through scaling circuits with a gains of 1/2 and -1/2 that are then connected to the AD9963's AUXIO pins. The monitoring function is useful for detecting supply overcurrent and / or short circuits in the circuit being powered.

Figure 19. User supply signals division

The positive supply monitoring signal is obtained with a resistive divider with a gain of 1/2 and the negative supply monitor signal is obtained with an inverting amplifier with gain -1/2:

There are 3 voltage rails in the positive analog section derived from the main USB connector or auxiliary USB power connector. An ADP2370 synchronous buck regulator provides the 3.3V voltage rail. This is a high efficiency, low quiescent current dc-to-dc converter which uses a proprietary high speed current mode and constant frequency PWM control scheme for excellent stability and transient response. This rail is used to supply the clock generator, the ADC drivers and the current-to-voltage converters of the AWG front end.

Figure 20. 3.3 V positive voltage rail

An ADP1614 step-up converter provides the 6V voltage rail. This is a dc-to-dc switching converter with an integrated power switch capable of providing an output voltage up to 20V. The device operates in a current-mode pulse-width modulation with up to 94% efficiency. Due to this architecture is allowed excellent transient response and easy noise filtering. This rail is used to supply the user power supply amplifiers, the switches used in the input signal chain, and the amplifiers of the AWG front end.

Figure 21. 6 V positive voltage rail

An LT1761 LDO Micropower Regulator provides the low-noise 4V rail used to supply the amplifiers from the buffer stage of the input signal chain. This is a low dropout regulator with low quiescent and shutdown current and with an input voltage range of 1.8V to 20V, output current of 100mA, and a dropout voltage of 300mV.

Figure 22. 4 V positive voltage rail

The negative analog section has 3 voltage rails, -6V, -3.3V and -5V. An ADP5074 inverting regulator provides -6V from the 5V USB input. It has a wide input voltage range (from 2.85V to 15V) and its integrated main switch enables the generation of an adjustable negative output down to 39V below the input voltage. This rail is used to supply the amplifiers of the user power supplies, the switches used in the input signal chain, and the amplifiers of the AWG front end.

Figure 23. -6 V voltage rail

An ADP7182 regulates the -6V rail to -3.3V. This device is is a CMOS, low dropout (LDO) linear regulator that operates from −2.7 V to −28 V and provides up to −200 mA of output current. This rail is used to supply the ADC drivers and the current-to-voltage converters of the AWG front end.

Figure 24. -3.3 V voltage rail

An LT1964ES5-5 provides the -5V rail. This device is a low-noise, Low Dropout Negative micropower Regulator with a fixed output voltage of -5V capable of supplying 200mA of output current. This rail is used to supply the amplifiers from the buffer stage of the input signal chain.

Figure 25. -5 V voltage rail

There are 4 supply rails for the digital section of the board. These rails are provided by two ADP2114 Dual Step-Down DC-to-DC Regulators. This device is a synchronous step-down switching regulator with two independent outputs.

It provides high efficiency(up to 95%) and operates at switching frequencies up to 2MHz. The input voltage range is 2.75V to 5.5V and the output is either fixed or adjustable.

One of the ADP2114s is used to provide 1.8V for the ADC/DAC and 1.35V for the DDR3 memory.

Figure 26. 1.8V and 1.35 digital voltage rail

The other ADP2114 is used to provide the 1.0V VCCPINT rail, which supplies the SoC, and the 3.3V rail which supplies the ADC and DACs.

Figure 27. 1V and 3.3V digital voltage rail

A Microchip USB3320 Hi-Speed USB 2.0 transceiver provides a USB PHY and ULPI connectivity to the SoC. The USB interface provides the following functions:

192.168.2.1 IP address by default.Figure 28. Usb PHY

System memory is a Micron MT41K256M16TW-107 4Gbit (512 MByte), 1066 Mbps, DDR3L low voltage SDRAM. This memory is used for temporary storage of streaming data as well as the operating system.

Figure 29 . DDR3 memory

Firmware is stored in a Micron MT25QU256ABA8E12-1SIT 265Mbyte, 90MBps Serial Flash. This device has an endurance of 100,000 ERASE cycles minimum (don't update the firmware more times than this).

Figure 30. Flash memory

A Xilinx Zynq XC7Z010-1CLG225C System on Chip provides processing and programmable logic functionality with the following specifications:

Additional information may be found at Zynq-7000 All Programmable SoC Overview and Datasheet

The board is completely self powered from USB and has two USB connectors: One for power and data and one for optional power.

Figure 31. USB connectors

Bus power from both USB connectors are pass through an LTC4415 dual monolithic ideal diodes with adjustable current limit, where the data USB bus current limit is set to 1A and the power USB bus current limit is set to 2A.

The two ideal diodes are independently enabled and prioritized using inputs EN1 and /EN2 such that the power USB connector has the higher priority.

Figure 32. Power selector

Analog Inputs

Signal Generator

Pattern Generator

Logic Analyzer

Digital I/O

Power Supplies

Network Analyzer

Voltmeter

Spectrum Analyzer

Other Features

Other Resources