Various levels of testbenches are available from component level to system level covering the whole stack including physical layer, link layer and transport layer components.

The component level testbnenches are located in the hdl repository, near to the JESD204 IPs itself in the tb folder.

The simulator can be selected through the SIMULATOR environment variable. Supported values are:

| $SIMULATOR | Simulator name |

|---|---|

| modelsim | Menthor/Siemens ModelSim/QuestaSim |

| xsim | Xilinx Vivado |

| xcelium | Cadence Xcelium |

| (default) | Icarus Verilog (iverilog) |

The system level testbenches reside in a separate github repository: testbenches repo

The test environment is built around Xilinx AXI VIPs so the only supported simulator is:

- Xilinx Vivado matching the current hdl release version requirements

jesd_loopback - A generic testbench covering the ADI JESD framework physical layer, link layer and transport layer components, supporting 204B or 204C 64b66b operation modes.

jesd_loopback_64b - A JESD testbench with Xilinx PHY supporting only the 64b66b mode

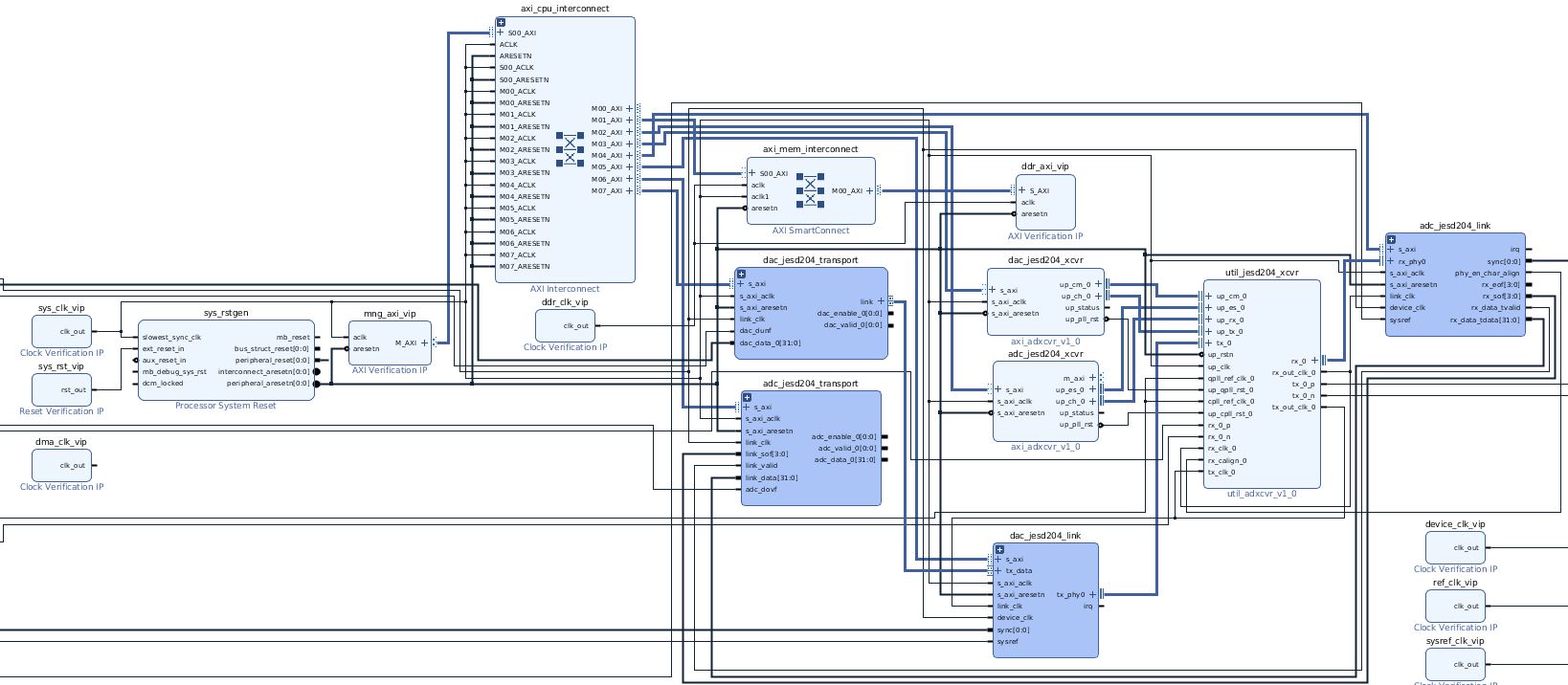

The devices under test (jesd204 components) are placed in a test harness which is made of several Xilinx verification IP's: clock and reset generators, AXI verification IPs to emulate the control side of the processor or to emulate a DDR storage module.

Details on running the testbench you can find in the README.md of each testbench and in the general README.md of the repository.

Analog Devices will provide limited online support for anyone using the core with Analog Devices components (ADC, DAC, Clock, etc) via the EngineerZone under the GPL license. If you would like deterministic support when using this core with an ADI component, please investigate a commercial license. Using a non-ADI JESD204 device with this core is possible under the GPL, but Analog Devices will not help with issues you may encounter.