This version (10 Sep 2013 14:26) is a draft.

This version (10 Sep 2013 14:26) is a draft.

This is an old revision of the document!

This document presents the steps to setup an environment for using the EVAL-AD5449SDZ evaluation board together with the Xilinx KC705 FPGA board and the Xilinx Embedded Development Kit (EDK). Below is presented a picture of the EVAL-AD5449SDZ Evaluation Board with the Xilinx KC705 board.

For component evaluation and performance purposes, as opposed to quick prototyping, the user is directed to use the part evaluation setup. This consists of:

The SDP-B controller board is part of Analog Devices System Demonstration Platform (SDP). It provides a high speed USB 2.0 connection from the PC to the component evaluation board. The PC runs the evaluation software. Each evaluation board, which is an SDP compatible daughter board, includes the necessary installation file required for performance testing.

Note: it is expected that the analog performance on the two platforms may differ.

Below is presented a picture of SDP-B Controller Board with the EVAL-AD5449SDZ Evaluation Board.

The AD5425 is a CMOS, 8-bit, current output digital-to-analog converter that operates from a 2.5 V to 5.5 V power supply, making it suitable for battery-powered applications and many other applications.

The EVAL-AD5449 evaluation board is designed to help customers quickly prototype new AD5425 circuits and reduce design time. The board requires ±12 V and +5 V supplies. The +12 V VDD and -12 V VSS are used to power the output amplifier; the +5 V supply is used to power the DAC (VDD) and transceivers (VCC).

The first objective is to ensure that you have all of the items needed and to install the software tools so that you are ready to create and run the evaluation project.

Before connecting the ADI evaluation board to the Xilinx KC705 make sure that the VADJ_FPGA voltage of the KC705 is set to 3.3V. For more details on how to change the setting for VADJ_FPGA visit the Xilinx KC705 product page.

To power on the EVAL-AD5449 evaluation board, you need to provide external +12V VDD and -12V VSS supply voltage used to power the output amplifier (for more information see: EVAL-AD5449SDZ evaluation board user guide) and a +5V supply used to power the DAC and transceivers.

For a quick start evaluation, run the download.bat script located in the SDK/SDK_Workspace/bin folder provided within the Reference Design Files. This script uses XMD to program the FPGA with the HDL Reference Design and download the Software Reference Design into the DDR.

The download.bat script assumes that the Xilinx ISE Design Suite 14.6 is installed at this path: C:/Xilinx/14.6. If the installation path on your computer is different, please modify the script accordingly.

If programming was successful, you should be seeing the command messages appear on the terminal.

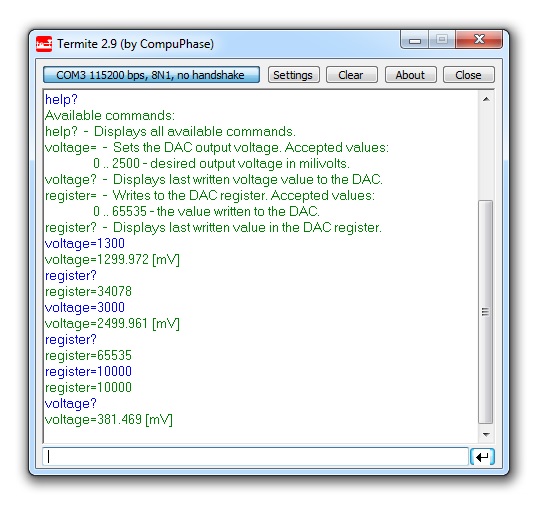

The following commands were implemented in this version of EVAL-AD5425 reference project for Xilinx KC705 FPGA board.

| Command | Description |

|---|---|

| help? | Displays all available commands. |

| register= | Loads selected DAC input register with a given value. Accepted value: 0 .. 255 - value to be written in register. |

| ldacPin= | Sets the output value of LDAC pin. Accepted values: 0 - sets LDAC pin low.(default) 1 - sets LDAC pin high. |

| ldacPin? | Displays the value of LDAC pin. |

Commands can be executed using a serial terminal connected to the UART peripheral of Xilinx KC705 FPGA.

The following image shows a generic list of commands in a serial terminal connected to Xilinx KC705 FPGA's UART peripheral.

The hardware platform for each reference projects with FMC-SDP interposer and KC705 evaluation board is common. The next steps should be followed to recreate the software project of the reference design: