This is an old revision of the document!

Direct digital synthesis

The direct digital synthesis (DDS) is used to generate sine-waves on a clock(referenced to sampling clock).

Typically, in the reference designs each HDL DAC interface IP has a DDS for every channel.

The resulting sine-wave can be changed at run time by 3 parameters:

clock frequency (sampling rate)

frequency word (FW)

phase shift

scale (the peak to peak amplitude of the sine-wave)

DDS basics

A generic DDS consists of a phase accumulator and a phase to amplitude converter.

The phase accumulator is basically a counter that increments by a frequency word which determines a timely overflow(the actual period of the signal).

The phase to amplitude convertor is a bit more complex and is the main consumer of FPGA resources out of the DDS modules.

Currently in the reference designs there are support two types of phase to amplitude converters, polynomial and CORDIC. The polynomial type uses more DSPs and less LUTs and FFs than the CORDIC, but at the cost of precision compared to the CORDIC.

ADI DDS module

Parameters

| Name | Description | Default Value |

DISABLE | Disable DDS | 0 |

DDS_DW | DDS out data bus width range 8-24 | 16 |

PHASE_DW | DDS phase accumulator data width. | 16 |

DDS_TYPE | 1 for CORDIC or 2 for Polynomial. | 1 |

CORDIC_DW | CORDIC stages data width, range 8-24 | 16 |

CORDIC_PHASE_DW | Number of CORDIC stages, range 8-24 (make sure CORDIC_PHASE_DW < CORDIC_DW) | 16 |

CLK_RATIO | The clock radtio between the device clock(sample rate) and the dac_core clock. | 0 |

Interface

| Interface | Type | Description |

clk | input | Input clock |

dac_dds_format | input | Two's complement(0) or offset binary(1) |

dac_data_sync | input | Data sync/external phase sync |

dac_valid | input | Valid signal(ready for new data) |

tone_1_scale | input[15:0] | Tone 1 scale |

tone_2_scale | input[15:0] | Tone 2 scale |

tone_1_init_offset | input[15:0] | Tone 1 initial offset(phase shift) |

tone_2_init_offset | input[15:0] | Tone 2 initial offset(phase shift) |

tone_1_freq_word | input[15:0] | Tone 1 frequency word |

tone_2_freq_word | input[15:0] | Tone 2 frequency word |

dac_dds_data | output[DDS_DW*CLK_RATIO-1:0] | Out sine-wave |

In the reference designs the DDS is controlled through the register map(dac channel section).

In the register map you cand find the formulas for:

scale = DDS_SCALE*

phase shift = DDS_INIT*

frequency word = DDS_INCR*

DAC Channel (axi_ad*)

Click to expand regmap

| Address | Bits | Name | Type | Default | Description |

| DWORD | BYTE |

| 0x0100 | 0x0400 | REG_CHAN_CNTRL_1 | DAC Channel Control & Status (channel - 0) |

| | | [21:16] | DDS_PHASE_DW[5:0] | R | 0x0000 | The DDS phase data width offers the HDL parameter configuration with the same name. This information is used in conjunction with REG_CHAN_CNTRL_9 and REG_CHAN_CNTRL_10. More info at https://wiki.analog.com/resources/fpga/docs/dds |

| [15:0] | DDS_SCALE_1[15:0] | RW | 0x0000 | The DDS scale for tone 1. Sets the amplitude of the tone. The format is 1.1.14 fixed point (signed, integer, fractional). The DDS in general runs on 16-bits, note that if you do use both channels and set both scale to 0x4000, it is over-range. The final output is (tone_1_fullscale * scale_1) (tone_2_fullscale * scale_2). NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0101 | 0x0404 | REG_CHAN_CNTRL_2 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_1[15:0] | RW | 0x0000 | The DDS phase initialization for tone 1. Sets the initial phase offset of the tone. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

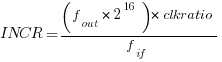

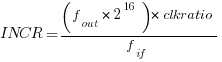

| [15:0] | DDS_INCR_1[15:0] | RW | 0x0000 | Sets the frequency of the phase accumulator. Its value can be calculated by  ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 1 is extended in REG_CHAN_CNTRL_9. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 1 is extended in REG_CHAN_CNTRL_9. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0102 | 0x0408 | REG_CHAN_CNTRL_3 | DAC Channel Control & Status (channel - 0) |

| | | [15:0] | DDS_SCALE_2[15:0] | RW | 0x0000 | The DDS scale for tone 2. Sets the amplitude of the tone. The format is 1.1.14 fixed point (signed, integer, fractional). The DDS in general runs on 16-bits, note that if you do use both channels and set both scale to 0x4000, it is over-range. The final output is (tone_1_fullscale * scale_1) + (tone_2_fullscale * scale_2). NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0103 | 0x040c | REG_CHAN_CNTRL_4 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_2[15:0] | RW | 0x0000 | The DDS phase initialization for tone 2. Sets the initial phase offset of the tone. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase init for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| [15:0] | DDS_INCR_2[15:0] | RW | 0x0000 | Sets the frequency of the phase accumulator. Its value can be calculated by  ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; where f_out is the generated output frequency, and f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. If DDS_PHASE_DW is greater than 16(from REG_CHAN_CNTRL_1), the phase increment for tone 2 is extended in REG_CHAN_CNTRL_10. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0104 | 0x0410 | REG_CHAN_CNTRL_5 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_PATT_2[15:0] | RW | 0x0000 | The DDS data pattern for this channel. |

| [15:0] | DDS_PATT_1[15:0] | RW | 0x0000 | The DDS data pattern for this channel. |

| 0x0105 | 0x0414 | REG_CHAN_CNTRL_6 | DAC Channel Control & Status (channel - 0) |

| | | [2] | IQCOR_ENB | RW | 0x0 | if set, enables IQ correction. NOT-APPLICABLE if DAC_DP_DISABLE is set (0x1). |

| [1] | DAC_LB_OWR | RW | 0x0 | If set, forces DAC_DDS_SEL to 0x8, loopback If DAC_LB_OWR and DAC_PN_OWR are both set, they are ignored |

| [0] | DAC_PN_OWR | RW | 0x0 | IF set, forces DAC_DDS_SEL to 0x09, device specific pnX If DAC_LB_OWR and DAC_PN_OWR are both set, they are ignored |

| 0x0106 | 0x0418 | REG_CHAN_CNTRL_7 | DAC Channel Control & Status (channel - 0) |

| | | [3:0] | DAC_DDS_SEL[3:0] | RW | 0x00 | Select internal data sources (available only if the DAC supports it).

- 0x00: internal tone (DDS)

- 0x01: pattern (SED)

- 0x02: input data (DMA)

- 0x03: 0x00

- 0x04: inverted pn7

- 0x05: inverted pn15

- 0x06: pn7 (standard O.150)

- 0x07: pn15 (standard O.150)

- 0x08: loopback data (ADC)

- 0x09: pnX (Device specific e.g. ad9361)

- 0x0A: Nibble ramp (Device specific e.g. adrv9001)

- 0x0B: 16 bit ramp (Device specific e.g. adrv9001)

|

| 0x0107 | 0x041c | REG_CHAN_CNTRL_8 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | IQCOR_COEFF_1[15:0] | RW | 0x0000 | IQ correction (if equipped) coefficient. If scale & offset is implemented, this is the scale value and the format is 1.1.14 (sign, integer and fractional bits). If matrix multiplication is used, this is the channel I coefficient and the format is 1.1.14 (sign, integer and fractional bits). NOT-APPLICABLE if IQCORRECTION_DISABLE is set (0x1). |

| [15:0] | IQCOR_COEFF_2[15:0] | RW | 0x0000 | IQ correction (if equipped) coefficient. If scale & offset is implemented, this is the offset value and the format is 2's complement. If matrix multiplication is used, this is the channel Q coefficient and the format is 1.1.14 (sign, integer and fractional bits). NOT-APPLICABLE if IQCORRECTION_DISABLE is set (0x1). |

| 0x0108 | 0x0420 | REG_USR_CNTRL_3 | DAC Channel Control & Status (channel - 0) |

| | | [25] | USR_DATATYPE_BE | RW | 0x0 | The user data type format- if set, indicates big endian (default is little endian). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [24] | USR_DATATYPE_SIGNED | RW | 0x0 | The user data type format- if set, indicates signed (2's complement) data (default is unsigned). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [23:16] | USR_DATATYPE_SHIFT[7:0] | RW | 0x00 | The user data type format- the amount of right shift for actual samples within the total number of bits. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [15:8] | USR_DATATYPE_TOTAL_BITS[7:0] | RW | 0x00 | The user data type format- number of total bits used for a sample. The total number of bits must be an integer multiple of 8 (byte aligned). NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [7:0] | USR_DATATYPE_BITS[7:0] | RW | 0x00 | The user data type format- number of bits in a sample. This indicates the actual sample data bits. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| 0x0109 | 0x0424 | REG_USR_CNTRL_4 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | USR_INTERPOLATION_M[15:0] | RW | 0x0000 | This holds the user interpolation M value of the channel that is currently being selected on the multiplexer above. The total interpolation factor is of the form M/N. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| [15:0] | USR_INTERPOLATION_N[15:0] | RW | 0x0000 | This holds the user interpolation N value of the channel that is currently being selected on the multiplexer above. The total interpolation factor is of the form M/N. NOT-APPLICABLE if USERPORTS_DISABLE is set (0x1). |

| 0x010A | 0x0428 | REG_USR_CNTRL_5 | DAC Channel Control & Status (channel - 0) |

| | | [0] | DAC_IQ_MODE[0] | RW | 0x0 | Enable complex mode. In this mode the driven data to the DAC must be a sequence of I and Q sample pairs. |

| [1] | DAC_IQ_SWAP[1] | RW | 0x0 | Allows IQ swapping in complex mode. Only takes effect if complex mode is enabled. |

| 0x010B | 0x042c | REG_CHAN_CNTRL_9 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_1_EXTENDED[15:0] | RW | 0x0000 | The extended DDS phase initialization for tone 1. Sets the initial phase offset of the tone. The extended init(phase) value should be calculated according to DDS_PHASE_DW value from REG_CHAN_CNTRL_1 NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

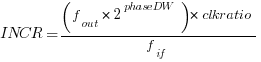

| [15:0] | DDS_INCR_1_EXTENDED[15:0] | RW | 0x0000 | Sets the frequency of tone 1's phase accumulator. Its value can be calculated by  ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_1 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_1 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x010C | 0x0430 | REG_CHAN_CNTRL_10 | DAC Channel Control & Status (channel - 0) |

| | | [31:16] | DDS_INIT_2_EXTENDED[15:0] | RW | 0x0000 | The extended DDS phase initialization for tone 2. Sets the initial phase offset of the tone. The extended init(phase) value should be calculated according to DDS_PHASE_DW value from REG_CHAN_CNTRL_2 NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

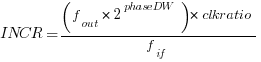

| [15:0] | DDS_INCR_2_EXTENDED[15:0] | RW | 0x0000 | Sets the frequency of tone 2's phase accumulator. Its value can be calculated by  ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_2 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). ; Where f_out is the generated output frequency, DDS_PHASE_DW value can be found in REG_CHAN_CNTRL_2 in case DDS_PHASE_DW is not 16, f_if is the frequency of the digital interface, and clock_ratio is the ratio between the sampling clock and the interface clock. NOT-APPLICABLE if DDS_DISABLE is set (0x1). |

| 0x0110 | 0x0440 | REG_* | Channel 1, similar to registers 0x100 to 0x10f. |

| 0x0120 | 0x0480 | REG_* | Channel 2, similar to registers 0x100 to 0x10f. |

| 0x01F0 | 0x07c0 | REG_* | Channel 15, similar to registers 0x100 to 0x10f. |

| Fri Sep 8 16:01:53 2023 | |

STRUCTURE

Below is the hierarchical structure of the modules.

ad_dds

ad_dds is the main module, it contains the phase accumulators and the phase to amplitude converters.

ad_dds_2

ad_dds_2 contains two phase to amplitude converters. The resulting wave-forms will be summed. The resulting wave-form must have a maximum amplitude level of 0x8000 -1. When only one tone is desired both tones must have the same frequency word and shift, there is no constraint for the amplitude, but if is equal for both channels, it should not be more than 0x400 -1 for each channel.

ad_dds_1

ad_dds_1 contains the phase to amplitude converter and an “amplifier”. The phase to amplitude converter is always generating a full scale sine-wave. Because the data format is two's complement, for a 16 bit data angle, min value will be -(2^16)/2 and max (2^16)/2-1.

ad_dds_sine_*

CLOCK RATIO

The clock ratio (number data paths processed in parallel) instantiates more DDS logic, but it it is controlled by the same register map for all CLOCK_RATIO/DATA_PATH parameters.

Where is the CLOCK_RATIO > 1? This scenario can be found in every high speed DAC design. It is required because the FPGA fabric can't work at the same speed than that of a high speed converter(typically > 250M).

Let's take the daq2(AD9144) as an example, where the clock ratio is 4, this ratio is chosen for the maximum sampling frequency 1GSPS, this results in an internal clock of 250MHz(device clock), which is closer to the upper limit of what some FPGAs can handle. So, in one clock cycle(250M) it needs to generate 4 consecutive samples in order to keep up with the DAC. This is done by 4 DDS modules. The phase accumulator part is all in one place and the phase to amplitude converters have dedicated sub-modules, as described above.

When the frequency is changed by software the 4 phases accumulator are align for the new frequency word and/or frequency phase shift. The counter increment value will be multiplied with clock ratio(4), to get a continuity of the 4 consecutive samples generated at t, t+1, t+2, and so on.

For scenarios where the synchronization signal comes from an external source and it is high for a longer period of time, the phase accumulator stages will be hold in reset, in order to avoid a noise like signal, caused by sending all the summed outputs of each DDS stage.

There is a minimum synchronization pulse width(delay) of n clock cycles, that is required to synchronize all phase accumulator stages, where n is equal to the CLK_RATIO.

In the above diagram example:

CLOCK_RATIO = 4

i0 = phase offset

i1 = i0 + FW

i2 = i1 + FW

i3 = i2 + FW

Each “i” is on 16 bits and each “s”(0-3) is on 64 bits.

i(t)+ is the value of the previous i(t) plus the increment(FW*CLOCK_RATIO).

It should be mentioned that after the phase init fall-edge, until the first valid sample, there is a delay caused by the phase to angle converter type and in the case of the CORDIC type, number of rotation stages will also have a direct impact on this clock period delay.

This version is outdated by a newer approved version.

This version is outdated by a newer approved version. This version (11 Oct 2021 16:01) was approved by Adrian Costina.The Previously approved version (08 Feb 2021 23:36) is available.

This version (11 Oct 2021 16:01) was approved by Adrian Costina.The Previously approved version (08 Feb 2021 23:36) is available.