This version (13 Jul 2023 21:15) was approved by Chance Fletcher.The Previously approved version (13 Jul 2023 18:54) is available.

This version (13 Jul 2023 21:15) was approved by Chance Fletcher.The Previously approved version (13 Jul 2023 18:54) is available.

This is an old revision of the document!

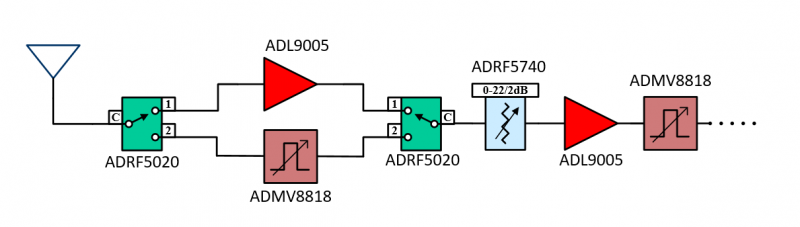

The 2-24GHz Receiver block diagram is shown below. The following wiki sections will go into more detail on the theory of operation of the individual, functional blocks of the signal chain.

The first stage of the Rx chain is the multi-mode input network (shown below), which can be configured for three different modes for quick performance optimization in a dynamic environment. The desired signal path is selectable via two ADRF5020 RF switches, which are capable of sub-100ns switching time and are controllable with GPIOs from the FPGA/ASIC.

The first mode enables an ADL9005 wideband LNA closest to the antenna, which provides the best possible NF across frequency and should be used as the default mode of operation. The second mode switches over to the ADMV8818 tunable filter configured to its full bypass state, effectively acting as an LNA bypass path. Transitioning from the LNA path to the filter path (in bypass mode) enables quick, front end gain reduction to react to high-power blockers potentially desensitizing the receiver. Finally, the third mode enables the ADMV8818 as a tunable pre-selector BPF, which is used here as an alternative to switched filter banks. This sub-octave, pre-selector filter path is used to address 2nd order intermod (IMD2) spurs that can show up when two out-of-band blocker spurs add or subtract to create a spur that falls in band, potentially masking the desired signal. Pre-selector filtering needs to be near the beginning of the signal chain adequately mitigate these interfering signals before they can hit a non-linear component such as an amplifier or mixer. Additionally, the ADMV8818 has independently configurable high and low pass filter bands to facilitate variable passband bandwidth- a frequent requirement of preselector filtering in wideband, tunable receiver signal chains. For example, the first band in a 2 to 24 GHz signal chain may only cover 2 to 3 GHz and would need good rejection at 1.5 GHz on the low side (F_high/2) and at 4 GHz on the high side (F_low*2). Whereas a higher band in the signal chain may cover 12 to 18 GHz, with good rejection required at 9 GHz on the low side and at 24 GHz on the high side. These differences mean many more filters are needed to cover lower frequencies bands than high frequency bands. A frequency spectrum example of the pre-selector filtering is shown in the following figure.

Following the switchable input network are an ADRF5740 digital step attenuator (DSA), LNA, and additional ADMV8818 tunable BPF. The ADRF5740 is one of two DSAs in the signal chain (with the other in the IF section), both of which serve multiple roles including gain levelling/control and NF/linearity optimization. This second ADMV8818 in the signal chain primarily acts as an image & IF rejection filter but can also provide some level of IMD2 mitigation if the LNA input path is used instead of the preselector filter path.

The image is a frequency band that, when present at the mixer input, will generate signals equal in amplitude to the desired signals at the mixer output. IF signal rejection is required to knock down spectrum at IF frequencies before the mixer to avoid them from leaking directly across the mixer and showing up as un-wanted spurs. A frequency spectrum example of the unwanted image and IF bands is shown below.

After the input network, the signal chain splits into two frequency conversion paths, each designed to translate a different frequency band of the RF input spectrum to an appropriate sampling IF. This architecture and frequency plan enables continuous frequency coverage across the entire 2-24GHz range by avoiding “dead zones” in coverage around the ADC Nyquist boundaries.

RF input frequencies above 6.5GHz (some coverage overlap with low-freq path) feed into an HMC8191 wideband I/Q mixer with a tunable LO source, downconverting the entire band to a final IF of 4-5GHz. Input frequencies below 7GHz feed into a more traditional, dual-stage heterodyne signal path- first running through an HMC773A upconverter to a high IF of 11-16GHz, then through the shared-path HMC8191 downconverter to a 4-5GHz IF. The lower-frequency path contains an additional amplifier to account for some of the extra conversion loss resulting from the two mixing stages, as well as 11-16GHz IF band-pass filtering to reject both the LO and the RF from leaking across the HMC773A mixer and into the downconverter. The figure below shows the frequency conversion section of the signal chain and the frequency operation ranges for each individual path.

The figure below provides an additional frequency plan visualization showing the individual frequency conversion steps for each frequency band.

The following table summarizes the possible frequency conversion paths:

Keysight SystemVue/Genesys was used to simulate different spurious signal rejection tests, namely IF rejection and image rejection tests. The test setup was similar for both tests - Our desired signal was injected at the input to the reciever chain, along with the undesired IF and image components for their respective tests. There are two paths a signal can take at the input of the receiver, one of which is for low noise performance and the other is for high spurious signal rejection performance. The low noise path utilizes an ADL9005 amplifier at the input of the chain to optimize noise performance of the front end, whereas the high rejection path implements an ADMV8818 bandpass filter to increase attenuation of undesired received signals.

Taking the low noise path, the average IF rejection performance was calculated to be 56.80dBc. The following plot shows the simulated IF rejection performance of the receiver front end in the low noise path:

Taking the high rejection path, the average rejection performance is improved by 58dB, giving an average rejection of 115.0788dBc. The following plot shows the IF rejection of the receiver front end in the high rejection path:

Taking the low noise path, the average image rejection performance was calculated to be 89.04dBc. The following plot shows the simulated image rejection performance of the receiver front end in the low noise path:

Taking the high rejection path, the average image rejection performance improved significantly to 160.7dBc. The following plot shows the simulated image rejection performance of the receiver front end in the high rejection path:

The IF section of the receiver front end, shown below, is the final stage before the ADC, performing additional signal conditioning and filtering. Two high-linearity amplifiers provide additional gain while the ADRF5730 DSA assists the DSA in the RF section with gain levelling/control and performance optimization in the IF. Anti-aliasing filtering is implemented by cascaded, COTS HPF and LPFs to provide 1GHz of IF bandwidth centered in the 2nd Nyquist band (4-5GHz) of the AD9082 sampling at 6GSPS.

The plot below shows the simulated frequency response of the IF section of the signal chain with the anti-aliasing filtering providing roughly 30-40dB of OOB (out-of-band) rejection around the sampled IF band. In general, anti-aliasing filtering should target 60dBc of OOB rejection, but satisfying this requirement with readily available COTS filters is somewhat impractical. It is recommended to use a custom anti-aliasing filter implementation if greater rejection is required by the end system.

Automatic gain control (AGC), RF path switching, and filter switching/reconfiguration often have critical timing specs that drive component selection, especially in systems that require fast frequency hopping or wideband tuning. The RF switches, DSAs, and tunable filters in the receiver signal chain offer fast switching/settling times, a high degree of configurability, and can be controlled via standard parallel and/or SPI interfaces. The ADMV8818 tunable filters also have the ability to store up to 128 filter states in an internal lookup as well as an internal state machine, allowing faster recall of preset filter configurations. The table below lists the control interfaces and minimum configuration and settling time details at the component level.

Keysight Systemvue/Genesys was used for detailed signal chain modelling and cascade analysis. Every component in the signal chain was modelled with frequency-dependent sys-parameter or s-parameter datasets to ensure accurate simulation results. The Genesys signal chain model shown below takes into account the following components:

To request the Keysight Pathwave simulation files that model the performance of these circuits, please send a request here and include the following info:

The Genesys workspace already has numerous system analysis and Matlab-based frequency sweeps in place, including the following functionality:

Receiver Performance (Gain, IIP3, IP1dB, NF, SFDR), 2-24GHz, LNA Path, Rough Gain Levelling Implemented

Receiver Performance (Gain, IIP3, IP1dB, NF, SFDR), 2-24GHz, Preselector BPF Path, Rough Gain Levelling Implemented

Receiver Performance vs Input Power Level with Gain Control, 10GHz, LNA Path