This document presents the steps to setup an environment for using the EVAL-CN0178-SDPZ evaluation board together with the Xilinx KC705 FPGA board and the Xilinx Embedded Development Kit (EDK). Below is presented a picture of the EVAL-CN0178-SDPZ Evaluation Board with the Xilinx KC705 board.

For component evaluation and performance purposes, as opposed to quick prototyping, the user is directed to use the part evaluation setup. This consists of:

The SDP-B controller board is part of Analog Devices System Demonstration Platform (SDP). It provides a high speed USB 2.0 connection from the PC to the component evaluation board. The PC runs the evaluation software. Each evaluation board, which is an SDP compatible daughter board, includes the necessary installation file required for performance testing.

Note: it is expected that the analog performance on the two platforms may differ.

Below is presented a picture of SDP-B Controller Board with the EVAL-CN0178-SDPZ Evaluation Board.

The CN0178 circuit uses the ADL5902 TruPwr™ detector to measure the rms signal strength of RF signals with varying crest factors (peak-to-average ratio) over a dynamic range of approximately 65 dB and operates at frequencies from 50 MHz up to 9 GHz.

The measurement result is provided as serial data at the output of a 12-bit ADC (AD7466).

The ADL5902 is a true rms responding power detector that has a 65 dB measurement range when driven with a single-ended 50 O source. This feature makes the ADL5902 frequency versatile by eliminating the need for a balun or any other form of external input tuning for operation up to 9 GHz. The ADL5902 provides a solution in a variety of high frequency systems requiring an accurate measurement of signal power. Requiring only a single supply of 5 V and a few capacitors, it is easy to use and capable of being driven single-ended or with a balun for differential input drive. The ADL5902 can operate from 50 MHz to 9 GHz and can accept inputs from -62 dBm to at least +3 dBm with large crest factors, such as GSM, CDMA, W-CDMA, TD-SCDMA, WiMAX, and LTE modulated signals.

The AD7466 is 12-bit, high speed, low power, successive approximation analog-to-digital converter (ADC). The part operates from a single 1.6 V to 3.6 V power supply and feature throughput rates up to 200 kSPS with low power dissipation. The part contains a low noise, wide bandwidth track-and-hold amplifier, which can handle input frequencies in excess of 3 MHz.

The EVAL-CN0178-SDP board contains the circuit to be evaluated, as described in this note. To power the EVAL-CN0178C-SDP evaluation board supply +6V between the +6 V and GND inputs.

The first objective is to ensure that you have all of the items needed and to install the software tools so that you are ready to create and run the evaluation project.

Before connecting the ADI evaluation board to the Xilinx KC705 make sure that the VADJ_FPGA voltage of the KC705 is set to 3.3V. For more details on how to change the setting for VADJ_FPGA visit the Xilinx KC705 product page.

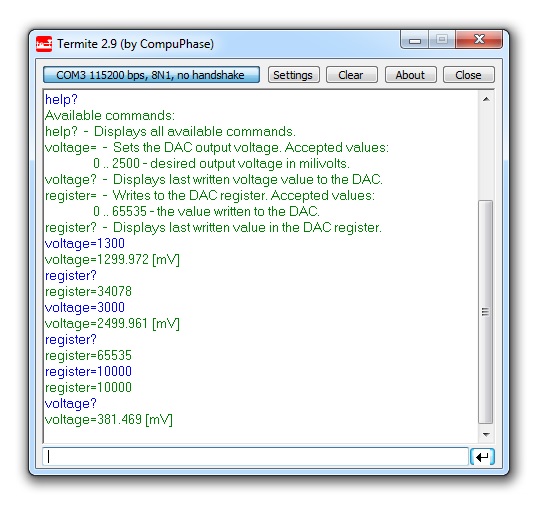

The following commands were implemented in this version of EVAL-CN0178 reference project for Xilinx KC705 FPGA board.

| Command | Description |

|---|---|

| help? | Displays all available commands. |

| calibration= | Makes a four points calibration. Accepted values: power input1(lowest value): -60 .. 0 - first point input power in [dBm]. power input2: -60 .. 0 - second point input power in [dBm]. power input3: -60 .. 0 - third point input power in [dBm]. power input3(highest value): -60 .. 0 - fourth point input power in [dBm]. |

| pinCalc? | Displays the calculated input power in [dBm]. |

| error? | Displays the error associated with the last input power calculation. Accepted values: -60 .. 0 - true input power in [dBm]. |

Commands can be executed using a serial terminal connected to the UART peripheral of Xilinx KC705 FPGA.

The following image shows a generic list of commands in a serial terminal connected to Xilinx KC705 FPGA's UART peripheral.

The hardware platform for each reference projects with FMC-SDP interposer and KC705 evaluation board is common. The next steps should be followed to recreate the software project of the reference design: