This document presents the steps to setup an environment for using the EVAL-CN0204-SDPZ evaluation board together with the Xilinx KC705 FPGA board and the Xilinx Embedded Development Kit (EDK). Below is presented a picture of the EVAL-CN0204-SDPZ Evaluation Board with the Xilinx KC705 board.

For component evaluation and performance purposes, as opposed to quick prototyping, the user is directed to use the part evaluation setup. This consists of:

The SDP-B controller board is part of Analog Devices System Demonstration Platform (SDP). It provides a high speed USB 2.0 connection from the PC to the component evaluation board. The PC runs the evaluation software. Each evaluation board, which is an SDP compatible daughter board, includes the necessary installation file required for performance testing.

Note: it is expected that the analog performance on the two platforms may differ.

Below is presented a picture of SDP-B Controller Board with the EVAL-CN0204-SDPZ Evaluation Board.

The EVAL-CN0204-SDPZ board provides a full function, high voltage (up to 44 V), flexible, programmable analog output solution that meets most requirements for programmable logic controller (PLC) and distributed control system (DCS) applications. When using this evaluation board with the SDP board or BeMicro SDK board, apply +6 V and GND to Connector CN2, 12-50 V and GND to Connector CN3.

The AD5662 low power (0.75 mW typical @ 5 V), rail-to-rail output, 16-bit nanoDAC® device and the AD5751 industrial current/voltage output driver are well matched with respect to input and output voltage ranges, as well as reference voltage requirements.

The AD5662, a member of the nanoDAC family, is a low power, single, 16-bit buffered voltage-out DAC that operates from a single 2.7 V to 5.5 V supply and is guaranteed monotonic by design.

The AD5662 requires an external reference voltage to set the output range of the DAC. The part incorporates a power-on reset circuit that ensures the DAC output powers up to 0 V (AD5662x-1) or to midscale (AD5662x-2), and remains there until a valid write takes place. The part contains a power-down feature that reduces the current consumption of the device to 480 nA at 5 V and provides software-selectable output loads while in power-down mode.

The low power consumption of this part in normal operation makes it ideally suited to portable battery-operated equipment. The power consumption is 0.75 mW at 5 V, going down to 2.4 μW in power-down mode. The AD5662’s on-chip precision output amplifier allows rail-to-rail output swing to be achieved. For remote sensing applications, the output amplifier’s inverting input is available to the user.

The AD5751 is a single-channel, low cost, precision, voltage/ current output driver with hardware or software programmable output ranges. The software ranges are configured via an SPI-/ MICROWIRE™-compatible serial interface. The AD5751 targets applications in PLC and industrial process control. The analog input to the AD5751 is provided from a low voltage, single-supply digital-to-analog converter (DAC) and is internally conditioned to provide the desired output current/voltage range.

The output current range is programmable across three current ranges: 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA.

Voltage output is provided from a separate pin that can be configured to provide 0 V to 5 V, 0 V to 10 V, and 0 V to 40 V output ranges. An overrange is available on the voltage ranges. Analog outputs are short-circuit and open-circuit protected and can drive capacitive loads of 1 μF and inductive loads of 0.1 H.

The device is specified to operate with a power supply range from 10.8 V to 55 V. Output loop compliance is 0 V to AVDD − 2.75 V.

The flexible serial interface is SPI and MICROWIRE compatible and can be operated in 3-wire mode to minimize the digital isolation required in isolated applications. The interface also features an optional PEC error checking feature using CRC-8 error checking, useful in industrial environments where data communication corruption can occur.

The device also includes a power-on reset function ensuring that the device powers up in a known state (0 V or tristate) and an asynchronous CLEAR pin that sets the outputs to zero-scale/midscale voltage output or the low end of the selected current range. An HW SELECT pin is used to configure the part for hardware or software mode on power-up.

The first objective is to ensure that you have all of the items needed and to install the software tools so that you are ready to create and run the evaluation project.

Before connecting the ADI evaluation board to the Xilinx KC705 make sure that the VADJ_FPGA voltage of the KC705 is set to 3.3V. For more details on how to change the setting for VADJ_FPGA visit the Xilinx KC705 product page.

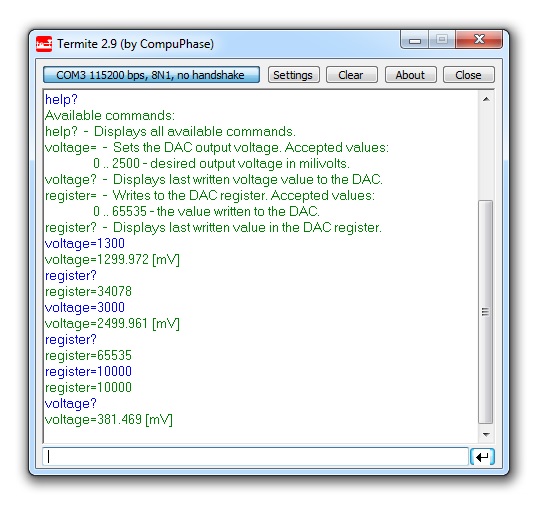

The following commands were implemented in this version of EVAL-CN0204 reference project for Xilinx KC705 FPGA board.

| Command | Description |

|---|---|

| help? | Displays all available commands. |

| register= | Write a value to the DAC register. Accepted values: 0 .. 65535 - value to be written in register. |

| register? | Displays the last value written to the DAC register. |

| ad5751clrPin= | Sets the output value of CLR pin. Accepted values: 0 - sets the CLR pin low.(default) 1 - sets the CLR pin high. |

| ad5751clrPin? | Displays the output value of CLR pin. |

| addressA0= | Sets the value of A0 address bit(JP1). Accepted values: 0 - address is 0b000.(default) 1 - address is 0b001. |

| addressA0? | Displays the value of A0 address bit(JP1). |

| range= | Sets the output range for AD5751. Accepted values: 0 → 0V to 5V. 1 → 0V to 10V. 2 → 0V to 6V. 3 → 0V to 12V. 4 → 0V to 40V. 5 → 0V to 44V. 6 → 4mA to 20mA(external). 7 → 4mA to 20mA(internal). 8 → 0mA to 20mA(external). 9 → 0mA to 20mA(internal). 10 → 0mA to 24mA(external). 11 → 0mA to 24mA(internal). 12 → 3.92mA to 20.4mA(internal). 13 → 0mA to 20.4mA(internal). 14 → 0mA to 24.5mA(internal). |

| range? | Displays the current output range. |

| fault? | Displays the list of possible faults. |

Commands can be executed using a serial terminal connected to the UART peripheral of Xilinx KC705 FPGA.

The following image shows a generic list of commands in a serial terminal connected to Xilinx KC705 FPGA's UART peripheral.

The hardware platform for each reference projects with FMC-SDP interposer and KC705 evaluation board is common. The next steps should be followed to recreate the software project of the reference design: