This is an old revision of the document!

SPI Engine Offload FPGA Peripheral

The SPI Engine Offload peripheral allows to store a SPI Engine command and SDO data stream in a RAM or ROM module. The command stream is executed when the trigger signal is asserted. This allows the execution of SPI transactions with a very short delay in reaction to a event.

Files

Configuration Parameters

| Name | Description | Default |

SPI_CLK_ASYNC | If set to 1 the ctrl_clk and spi_clk are assumed to be asynchronous | 0 |

CMD_MEM_ADDR_WIDTH | Configures the size of the command stream storage. The size is 2**CMD_MEM_ADDR_WIDTH entries. | 4 |

SDO_MEM_ADDR_WIDTH | Configures the size of the SDO data stream storage. The size is 2**SDO_MEM_ADDR_WIDTH entries. | 4 |

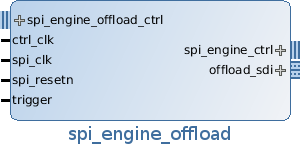

Signal and Interface Pins

| Name | Type | Description |

ctrl_clk | Clock | The spi_engine_offload_ctrl signals are synchronous to this clock. |

spi_clk | Clock | The spi_engine_ctrl siganls, offload_sdi signals and trigger are synchronous to this clock. |

spi_resetn | Synchronous active low reset | Resets the internal state machine of the core. |

trigger | Input | When asserted the stored command and data stream is send out on the spi_engine_ctrl interface. |

spi_engine_offload_ctrl | SPI Engine Offload Control Interface slave | Control interface which allows to re-program the stored command and SDO data stream. |

spi_engine_ctrl | SPI Engine Control Interface master | SPI Engine Control stream that contains commands and data. |

offload_sdi | Streaming AXI master | Output stream of the received SPI data |

Theory of Operation

This version (27 May 2015 14:19) is a draft.

This version (27 May 2015 14:19) is a draft.