This version (18 Mar 2022 18:12) was approved by Antonio Jimenez de Parga.

This version (18 Mar 2022 18:12) was approved by Antonio Jimenez de Parga.This is an old revision of the document!

Evaluation Board for the AD3542R, Dual Channel, 16-Bit, 16 MUPS, Multispan, Multi-IO SPI DAC

The EVAL-AD3542RFMCZ is an evaluation board for the AD3542R ultrafast 16-bit precision DAC.

The board allows testing all the output ranges of the DAC, waveform generation, power supply and reference options.

The EVAL-AD3542RFMCZ interfaces to the USB port of a PC via a system demonstration platform (SDP-H1 board). It can also be connected to a different controller board using the pin header connector at position P5.

This user guide covers the details of the configuration and operation of the EVAL-AD3542RFMCZ board and the associated ACE plug-in. For additional information on the DAC operation refer to the AD3542R data sheet.

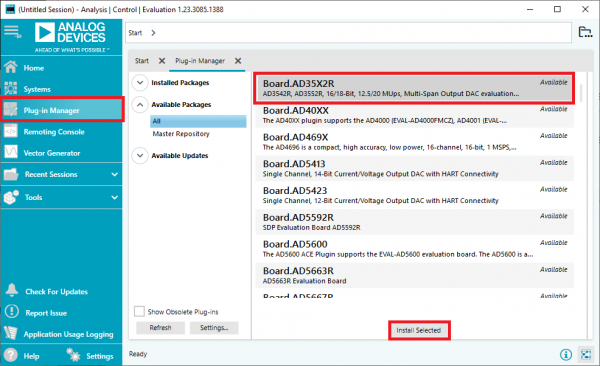

The EVAL-AD3542R uses the ACE software with the AD35X2R Plugin for evaluation.

Figure 1. Plug-in Manager

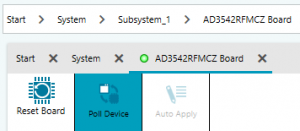

Figure 2. Start Tab

To set up the evaluation board, take the following steps:

The EVAL-AD3542R includes a complete power conversion solution to allow powering the evaluation board from the SDP-H1. The board includes a DC/DC converter LTC7149 to generate -7V from the 12V power provided by SDP-H1. LDOs LT3045 and LT3094 are used to generate the positive and negative supplies for the transimpedance amplifiers, which are selectable using switch S1. Additional LT3045 LDOs are used to generate the supplies for the logic and the DAC core of the AD3542R. This power solution is configured with the default link settings shown in Table 2.

Alternatively, the board can be powered from a collection of external power supplies via connector P3. The assignment of the pins in connector P3 is listed in Table 1.

| Pin Number | Signal | Description |

|---|---|---|

| 1 | EXT_PVDD | External positive supply for transconductance amplifiers. 4.7V to 10.6V ± 5%. |

| 2 | EXT_PVSS | External negative supply for transconductance amplifiers. 0V down to PVDD-10.6V ± 5%. |

| 3 | EXT_VDD | External analog supply for AD3542R. 5V ± 5%. |

| 4 | EXT_DVDD | External digital supply for AD3542R. 1.8V ± 5%. |

| 5 | EXT_VLOGIC | External digital I/O supply for AD3542R. 1.1V to 1.9V. |

| 6 | GND | Ground. |

The EVAL- AD3542R also integrates an on-board 2.5V analog reference ADR4525.

The supply for the transimpedance amplifier integrated in AD3542R must be adjusted depending on the selected output span using switch S1. Table 2 presents the three possible supply configurations. The correspondence with the output range is shown in Table 7.

| S1 Position | Label | PVDD Voltage | PVSS Voltage |

|---|---|---|---|

| Left | +/- 5V | 5.2V | -5.2V |

| Middle | 10V | 10.2V | -0.2V |

| Right | -2.5/7V | 7.7V | -2.7V |

The EVAL-AD3542R board is delivered with the links placed in the default positions listed in Table 3. This configuration is suitable for operating the board right out of the box. However, the links J_FB0, J_FB1 and J_REF may need to be adjusted depending on the configuration set in the registers of the AD3542R. Refer to Figure 3 to locate the position of links and connectors.

Figure 3. Board Layout

| Link | Silkscreen | Description | Default Position |

|---|---|---|---|

| J_FB0 | FB0 | This link selects the gain of transimpedance amplifier for channel 0. The gains are labeled x1 and x2 which corresponds to the multiplicative factor between them. The gain must be set in accordance to the desired output range listed in Table 6. Inserting the link allows selecting gains x1 or x2. | x1 |

| J_FB1 | FB1 | This link selects the gain of transimpedance amplifier for channel 0. The gains are labeled x1 and x2 which corresponds to the multiplicative factor between them. The gain must be set in accordance to the desired output range listed in Table 6. Inserting the link allows selecting gains x1 or x2. | x1 |

| J_OUT0 | J_OUT0 | This link bridges the output voltage of DAC0 to connector VOUT0 through the matching network R4, L5, R28, C15. When inserted, signal can be measured on connector VOUT0. When not inserted, signal can only be measured on test point TP2. | Inserted |

| J_OUT1 | J_OUT1 | This link bridges the output voltage of DAC1 to connector VOUT1 through the matching network R5, L6, R29, C16. When inserted, signal can be measured on connector VOUT1. When not inserted, signal can only be measured on test point TP3. | Inserted |

| J_REF | J_REF | This link allows connecting the on-board reference to AD3542R. This link should be removed if an external reference is provided via connector J1 (VREF) or if the internal reference is output to the VREF pin. | Inserted |

| J_PVDD | PVDD | This link selects the positive voltage supply for the transimpedance amplifier. REG selects the supply from the on-board LDO. EXT selects the supply provided externally on connector P3. | REG |

| J_PVSS | PVSS | This link selects the negative voltage supply for the transimpedance amplifier. REG selects the supply from the on-board LDO. EXT selects the supply provided externally on connector P3. GND sets the supply rail to ground. | REG |

| J_VDD | VDD | This link selects the voltage supply for the analog section of AD3542R. REG selects the 5V supply from the on-board LDO regulator. EXT selects the supply provided externally on connector P3. | REG |

| J_DVDD | DVDD | This link selects the voltage supply for the digital section of AD3542R. 1V8 REG selects the supply from the on-board LDO regulator. FPGA selects the supply provided from the SDP-H1 board, the same as used in the FPGA IO pins. EXT selects the supply provided externally on connector P3. | 1V8 REG |

| J_VIO | VLOGIC | This link selects the voltage supply for AD3542R IO pins. 1V8 REG selects the supply for the on-board LDO regulator. FPGA selects the supply provided from the SDP-H1 board, the same as used in the FPGA IO pins. EXT selects the supply provided externally on connector P3. | 1V8 REG |

| S1 | S1 | This switch selects one of the following combinations for PVDD and PVSS: • Left: PVDD = 5.2V, PVSS=-5.2V • Middle: PVDD = 10.2V, PVSS = -0.2V • Right: PVDD = 7.7V, PVSS = -2.7V | Left +/- 5V |

Table 4 shows the list of connectors available on EVAL-AD3542R and their corresponding use. Refer to Figure 3 to find their location in the board.

| Connector | Silkscreen | Signal Name | Function |

|---|---|---|---|

| J1 | VREF | VREF | Reference voltage input / output. This connector can be used to provide an external reference voltage to the AD3542R or to monitor the reference generated by ADR4525 or AD3542R. |

| J2 | CLOCK | CLOCK_FMC | External clock reference provided to the FPGA to generate the SPI patterns. 1.8V amplitude. |

| J3 | SYNC | SYNC_EVENTS | External trigger signal provided to the FPGA to synchronize waveform generation. 1.8V amplitude. |

| VOUT0 | VOUT0 | VOUT0_C | Voltage output of DAC channel 0. |

| VOUT1 | VOUT1 | VOUT1_C | Voltage output of DAC channel 1. |

| P1 | P1 | - | FMC connector carrying the digital signals between the evaluation board and the controller board. |

| P3 | P3 | - | External supply connector. Pin assignment given in Table 1. |

| P5 | P5 | - | Digital signal connector. This connector is used to control the AD3542R with a controller different from SDP-H1. The pin assignment is listed in Table 4. The pin header is not assembled by default so that the holes can be used as test points for the digital signals. |

Connector P5 is used to connect an external controller when the SDP-H1 is not present. This connector grants access to all the digital signals of AD3542R and some board supplies and control lines.

| Pin number | Connector Label | Function |

|---|---|---|

| 1 | +12V_FMC | External 12V power supply. Use this pin to supply the EVAL-AD3542R board when using a controller different from the SDP-H1. |

| 2 | POWER_ON_FMC | Enable signal for the onboard regulators. This pin is used to manually turn on the LDOs and DC/DC converter when the SDP-H1 controller is not present. Set a voltage higher than 1.24V to turn on. |

| 3 | GND | Ground. |

| 4 | SPI_QPI | Connected to FPGA. Not used. |

| 5 | VLOGIC | Voltage supply used for AD3542R I/O pins. If this pin is used to supply VLOGIC, remove the link for VLOGIC. |

| 6 | GND | Ground. |

| 7 | SPI_CS | SPI Chip Select signal. |

| 8 | SPI_SCLK | SPI clock signal. |

| 9 | GND | Ground. |

| 10 | SPI_SDIO0 | SDI / MOSI signal in Classic SPI mode or SDIO0 signal in Dual SPI mode. |

| 11 | GND | Ground. |

| 12 | SPI_SDIO1 | SDO / MISO signal in Classic SPI mode or SDIO1 signal in Dual SPI mode. |

| 13 | CLOCK_FMC | External clock signal (same as connector J2). |

| 14 | GND | Ground. |

| 15 | LDAC | AD3542R LDAC signal. |

| 16 | GND | Ground. |

| 17 | RESET | AD3542R RESET signal. |

| 18 | GND | Ground. |

| 19 | ALERT | AD3542R ALERT signal. |

| 20 | VLOGIC_FMC | Test Pin for VLOGIC_FMC power supplied from the SDP-H1. |

The board includes several test points to access relevant signals. Only TP4 has the test ring assembled. The list is given in Table 6.

| Test Point | Signal | Description |

|---|---|---|

| TP1 | VREF | Reference voltage for AD3542R (internal, on-board or external) |

| TP2 | VOUT0 | Voltage output of DAC channel 0 |

| TP3 | VOUT1 | Voltage output of DAC channel 1 |

| TP4 | GND | Ground |

| TP7 | GPIO_9 | Synchronization signal from FPGA for development purposes |

| TP8 | SYNC_EVENT | External trigger for waveform generation |

The selection of the output range requires a combination of register configurations and a given transimpedance gain. The supply of the transimpedance amplifier must be adjusted accordingly. The gains corresponding to each output range and the required board configuration are listed in Table 7. See the AD3542R datasheet for more details on output range configuration.

| CHx_OUTPUT_RANGE_SEL Field Value | Output Range | Transimpedance Gain Setting | S1 Setting | VZS (V) | VFS (V) |

|---|---|---|---|---|---|

| 000 | 2.5V | x1 | Any | -0.198 | 2.697 |

| 001 | 5V | x1 | Any | -0.077 | 5.076 |

| 010 | 10V | x2 | Middle | -0.163 | 10.163 |

| 011 | ±5V | x2 | Left | -5.163 | 5.166 |

| 100 | -2.5V to 7.5V | x2 | Right | -2.666 | 7.662 |

Monitoring the output of the DAC in dynamic conditions can become difficult because the amplifier is a low-impedance source driving a high-impedance load with a fast rising time. The EVAL-AD3542R allows using different passive networks to adapt the output of the DAC to different loads. The following configurations are foreseen:

ACE has several views to control different aspects of the DAC. When a view is first opened it creates a new tab at the top of the main window. The AD3542R plugin has a Board View, a Chip View, a Memory Map view, a Waveform Generator view, and a Vector Generator view. Figure 4 shows the hierarchical relation between these views. For additional information refer to the The user manual that is accessible from the help panel displayed when clicking on the Help button on the lower left angle of the application. There is also an ACE Wiki with additional information.

Figure 4. ACE Plugin Hierarchy

The board view displays a simplified diagram of the evaluation board including some relevant connectors and the interconnection between chips, as seen in Figure 5. Analog Devices chips are shown with their part number and the AD3542R is highlighted in darker blue.

Figure 5. AD3542R Board View

The actions that can be performed at this level are displayed as buttons at the top of the main window, as seen in Figure 6.

Figure 6. AD3542R Board View Buttons

To open the chip view, double-click on the AD3542R block.

The Chip View displays a simplified internal diagram of the chip showing the interface logic, the DAC cores, the precision feedback resistors and the relevant pins for those blocks. This view contains three interactive areas, as depicted in Figure 7:

Figure 7. Chip View

The Memory Map view displays the entire configuration space of the AD3542R. The configuration space can be displayed as a list of registers or as a list of bit fields. The application allows sorting by any of the column categories or searching by register name or field name. Registers can be displayed collapsed or expanded into its bit

fields, as shown in Figure 8.

This view has the following interactive elements:

Figure 8. AD3542R Memory Map View

The waveform generator view allows assigning vectors to the channels and starting or stopping waveform generation. A screenshot of this view is given in Figure 9.

Figure 9. Waveform Generator View

The operation mode of AD3542R and the assignment of the waveforms is controlled from the Transmit pane that contains the following controls:

| Fast Mode (16 bit) | Precision Mode (24 bit) | |

|---|---|---|

| Dual Channel Mode | 6.25 MUPS | 4.16 MUPS |

| Single Channel / Simultaneous Mode | 12.5 MUPS | 8.33 MUPS |

Figure 10. Waveform Generation in Dual Mode

Figure 11. Waveform Generation in Simultanoeus Mode

If the Auto Register Update checkbox is not checked, the streaming mode parameters have to be configured manually in the memory map before pressing the Play button. The following registers must be set:

| Fast Mode (16 bit) | Precision Mode (24 bit) | |

|---|---|---|

| Single Channel / Simultaneous Mode | 2 | 3 |

| Dual Channel Mode | 4 | 6 |

The Vector Generator view allows defining or loading waveforms that can later be assigned to the DAC channels. Waveforms are identified by name. The generator automatically adapts the sample rate based on the operating mode and the number of DAC channels enabled. A snapshot of this view if presented in Figure 12.

The Vector Generator tool is composed of the following sections:

Figure 12. Vector Generator View

Follow these steps to produce a dual waveform playback on the EVAL-AD3542R evaluation board:

Figure 13. Dual Waveform Output

The current version of EVAL-AD3542R ACE Plugin (1.2021.38200) does not support all the board features at the moment. ACE notifies when an update of the plugin is available, so these features will be progressively incorporated. These are the features not currently supported: