Note: if using the Xilinx KCU105 evaluation kit as a pattern generator, customers will need to purchase the following additional components:

The AD917x Evaluation Board Setup Guide provides details about how to set up the hardware and software for the evaluation kit. This guide explains how to setup the KCU105 and the ADS8 and AD917x-FMC-EBZ. This evaluation kit will also support the Analog Devices ADS7 platform for lane rate configurations that are ≤12.5Gbps. The DPGDownloader software will be used to set up the data vectors and FPGA SERDES mode configuration for the KCU105 platform, ADS8 or ADS7 and the ACE software (Analysis | Control | Evaluation) will be used to set up the AD917x evaluation board, including the HMC7044 clock distribution chip on the board. The AD917x-FMC-EBZ evaluation board can be driven by an external direct clock with DAC PLL off or the on-board clock from HMC7044 with DAC PLL on. The reference clock of HMC7044 can be provided by the on-board 122.88MHz crystal or the external signal generator.

The required software to run the evaluation board is as follows:

Once both programs are installed, launch ACE. On the start-up window, navigate to Tools → Manage Plugins. The plugin manager pop-up window will display. Search for AD9172 and select install plugin to install the appropriate plugin files for the FMC evaluation board.

From the factory, the AD917X-FMC-EBZ is configured to generate all necessary clocks using an on-board clocking IC, the HMC7044. Using PLL2, The HMC7044 generates the lanerate/40 clock, two phase-aligned SYSREF clocks, and a reference for the AD917x's on-chip PLL to generate a DAC sampling clock (DACCLK). The reference for PLL2 is an on-board, 122.88MHz VCXO. Using PLL1, the 122.88MHz VCXO can be locked to an external reference via an SMA port at J41.

For some configurations, the user may be interested to use a custom clock source and provide the DACCLK directly to the CLK± pins of the AD917x (whether or not using the DACCLK PLL). In this case, remove C36 and C38 and populated C34 and C35 instead, as shown in the Figure 4. Connect a high-performance clock with >=12dBm output level to J34.

Clocking for a JESD204B link

When using a JESD204B link to the AD917x, the JESD204B link clocks are generated by the HMC7044's PLL2. The HMC7044 should be frequency-locked to common reference with the DAC sampling clock, via HMC7044's PLL1. PLL1 can lock the onboard 122.88MHz VCXO to external reference, or to an onboard XTAL (also 122.88MHz). The reference must be an integer-multiple of 122.88MHz , such as 3.84MHz , 7.68MHz, 15.36MHz, 30.72MHz, 61.44MHz, 122.88MHz, 245.76MHz or 491.52MHz.

It is best to use a second, low phase noise, reference clock source with 0 dBm output level, connected to the SMA port at J41; the reference clock source must be frequency locked to a common reference with the DAC clock source. Two options exist: Two separate sources can be synchronized through the 10MHz INPUT/OUTPUT port in the back panel of the equipment; or alternatively, a unit such as the Rohde and Schwarz SMA100 has a convenient option for a secondary clock source, to generate the two external clocks from a single unit.

Clocking for NCO-only mode

When using the AD917x in NCO-only mode, without a JESD204B link, the only external clock needed is at J34. The HMC7044 is not used in this case.

The Cypress FX3 and interconnect board are not needed if the ADS7 or ADS8 board is used for data pattern generation. The hardware setup configuration when using the ADS7/ADS8 is as follows:

Figure 3. Evaluation Board Kit Components Hardware Connection Setup with ADS8-V1

Figure 3. Evaluation Board Kit Components Hardware Connection Setup with ADS8-V1

In order to operate the AD917x evaluation board with the Xilinx KCU105, the customer must acquire the following items:

Before connecting the hardware, the Cypress FX3 board and Micro SD Card must be programmed appropriately.

FX3 SDP Drivers: fx3_sdpdrivers_kcu105.zip

Begin by installing the FX3 SDP Drivers using the above link. When installing the drivers, ensure that the FX3 board is NOT plugged into your computer. A successful install will give an exit code of 256 in the printout while an unsuccessful install will try to restart your computer. If you experience an unsuccessful install, try re-running the driver installation executable. Some machines need to run this installer 3 times before the drivers are installed. You may receive a notification that newer drivers have already been installed—in this case, the installer will automatically abort installation as expected.

You can confirm proper installation by following these steps:

If you have confirmed successful driver installation, you can proceed to the next section which covers the FPGA image. If you do not see the device “High Speed Converter USB3.0 Evaluation Platform”, look for a device named “FX3” with a warning message. If you cannot locate the device “High Speed Converter USB3.0 Evaluation Platform” or the device “FX3”, try reinstalling the FX3 SDP Drivers.

Most FX3 boards come preprogrammed with ADI’s firmware, but there are some instances when this firmware is missing. If you have installed the FX3 SDP Drivers but only see an “FX3” device with a warning listed under Device Manager, then your FX3 board is not preprogrammed. In this case, follow these steps to program your FX3 board:

FX3 Firmware Image: fx3firmware_r2_06032016.zip

As described earlier, successful firmware installation can be confirmed by following these steps:

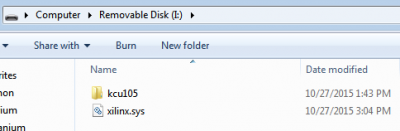

FPGA Image: kcu105_micro_sd_files.zip

Download the KCU105 FPGA image files and copy them to the MicroSD card so that the xilinx.sys file and kcu105 folder are at the top level of the MicroSD card:

Connect the boards and cables to the KCU105 board as shown in Figure 1 below.

Figure 1. Evaluation Board Kit Components Hardware Connection Setup

Figure 1. Evaluation Board Kit Components Hardware Connection Setup

Connect a reference clock frequency to the “Board Ref Clock” connection shown in Figure 1 (SMA connector J4). This is the configuration required any time the evaluation board is to be measured and used. Turn on the KCU105 power and plug in both USB cables to the host computer.

The KCU105 board requires some additional setup steps to be compatible with the DPGDownloader software, and these steps only need to be done once to properly configure the FPGA for future use with DPGDownloader. Before powering on the KCU105 unit, insert the Micro SD card with FPGA image into the appropriate slot on the bottom right-hand side of the KCU105 evaluation board as shown in Figure 1. Be certain to verify that the Micro SD card clicks into place when inserted. In order to boot up the KCU105 board using the image from the Micro SD card, ensure that the DIP switch settings on SW15 are set according to Figure 2 below.

Figure 2. KCU105 DIP Switch Settings for Loading Image from Micro-SD Card

Figure 2. KCU105 DIP Switch Settings for Loading Image from Micro-SD Card

Once these steps are complete, the KCU105 board can be powered on and plugged into the USB ports on the host PC. After powering on the KCU105, wait approximately 10 seconds so that the KCU105 has adequate time to load the FPGA image. If the KCU105's LEDs begin flashing immediately after power on, then the FPGA image has not been loaded correctly. In this case, remove the Micro SD card, confirm that the appropriate files are stored on the card, and repeat the above procedure. Be sure to verify that your Micro SD card is not being encoded when you write the FPGA image to it. Proper FPGA image programming can be confirmed by looking at the 3 LEDs near the KCU105's power switch--these 3 LEDs should be toggling in a heartbeat pattern.

The AD917x-FMC-EBZ complies with the VITA57.1 standard. Thus, the AD917x-FMC-EBZ can be used with any FMC-compliant FPGA development kit. The AD917x has a convenient crossbar switch, which allows to remap the physical lanes routed to its SERDESx+/- pins on the PCB (“physical lanes”) to the internal SERDES lanes within the JESD204B IP of the AD917x (“Logical lanes”). Any physical lane can be mapped to any of the logical lanes on-chip. For more details please refer to the Crossbar Switch section in the AD917x's datasheet.

The AD917x can work in NCO-only mode, without ADS7/ADS8/KCU105. In this case, DO NOT CONNECT the AD917x-FMC-EBZ board to the ADS7/ADS8/KCU105. Instead, connect an external +12V power supply to TP41 (red) and GND to TP42 (black). The external power supply should have capacity for at least 1A of current. Install the jumper on JP71 for powering on the PIC and USB port.

If using an external clock source, connect a low phase noise, high frequency clock source to J34. See the “Directly Clocking the AD917x-FMC-EBZ” section for more details.

The outputs of the AD917x can be captured at the SMA connectors: J1 for DAC0; J2 for DAC1; and J3 for CLKOUT.

Some applications may be more sensitive to clock spurious. To prevent any spurious coupling from the onboard HMC7044 onto the AD917x output, the HMC7044 may be kept in reset:

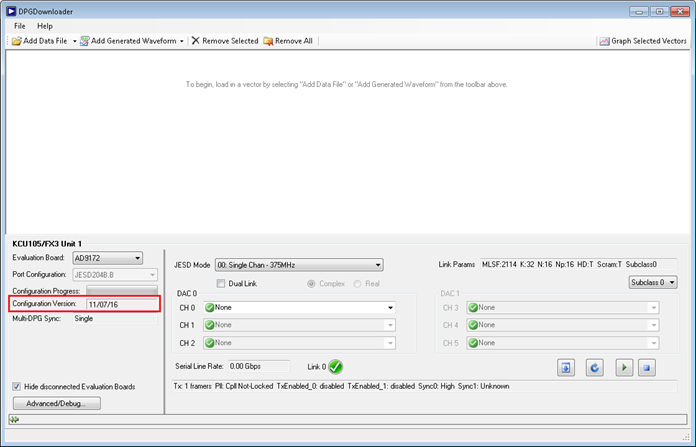

Launch the DPGDownloader software from the Start Menu (Start → All Programs → Analog Devices → DPG → DPG Downloader). When the program starts the DPG Panel should look recognize the evaluation board connected as shown in the AD917x panel being displayed as shown in Figure 5. The desired SERDES JESD204B mode can be selected by using the “JSED Mode” drop-down menu. If running in Dual Link mode, check the “Dual Link” checkbox on the panel to enable the second link options. Use the “Add Generated Waveform” drop-down menu to create vectors to send to the evaluation board as desired. Note: If using the KCU105, first power up the KCU105 board and wait for the heartbeat LEDs shown in Figure 1 to begin flashing. Then open up DPGDownloader and ensure the Configuration Version displays 11/07/16, confirming that the FPGA image is loaded properly from the microSD card. If this does not display or if the KCU105 has been powered off and back on again, reselect the AD917x from the Evaluation Board dropdown menu to reinitialize the panel and the configuration version should display properly.

Figure 5. DPGDownloader AD917x Panel

Figure 5. DPGDownloader AD917x Panel

Depending on the JESD Mode selected, different combinations of channels and DAC selection options become active on the GUI and allow for user input. The “Link Params” readback displays the JESD204B link parameters that are configured in the FPGA. The following GUI button controls operate as follows:

If a custom vector is to be used, the format of this vector will depend on the mode of operation chosen. If the mode chosen is a real mode (will display which mode type it is in the DPGDownloader panel), create separate I and Q vectors as desired and load them in individually to the desired DAC channels. If the mode chosen is a complex mode, the vector loaded into DPGDownloader should be one single vector that first has the I vector data then concatenate the Q vector data all into one file. Load this vector into the panel and then select the complex concatenated vector into the desired DAC channels.

To get the AD917x plugins, launch the ACE software from the Start Menu (Start → All Programs → Analog Devices → ACE → ACE) and select “Tools” → “Manage Plugins” or click the 'Plugin Manager Icon' in the bottom right-hand corner of the ACE application, shown in Figure 6. This will launch the plugin manager in ACE.

Figure 6. ACE Plugin Manager

Figure 6. ACE Plugin Manager

In the plugin manager, look under “Available Packages” for the Board.AD9172 plugins, select it and click “Install Selected”, shown in Figure 7.

Figure 7. Install AD917x Board Plugins

Figure 7. Install AD917x Board Plugins

Once the installation finishes click “Close” and you should see the AD917x-FMC-EBZ board plugin show up in the offline area for “Explore Local Plugins”. If the evaluation board is connected through USB, the ACE GUI should look recognize the AD917x-FMC-EBZ evaluation board connected as shown in Figure 8 in the “Attached Hardware” section. If it does not recognize the board immediately, try closing ACE after the installation is complete and relaunching and the software should bring up the board plugin with the version of the plugin that was installed displaying (Version 1.2.1.0 in this example shown).

Figure 9. AD917x-FMC-EBZ Board Plugin View with Startup Wizard

Figure 9. AD917x-FMC-EBZ Board Plugin View with Startup Wizard

By double-clicking on the AD917x-FMC-EBZ icon the board plugin view will be automatically displayed, as shown in Figure 9.The board view contains an easy Startup Wizard which allows the user to choose the different configurations for how to set up the AD917x (along with the HMC7044 clock chip) easily without manually programming the part. It supports both DC Test Mode functionality as well as SERDES interface functionality. The various sections of the wizard can be expanded or collapsed by pressing the ![]() or

or ![]() buttons.

The following GUI inputs are defined as follows:

buttons.

The following GUI inputs are defined as follows:

Board Clock Settings:

DC Test Mode:

SERDES Interface:

Clock Frequencies (Data/DAC/Lane Rates):

DAC PLL:

NCO Frequency Controls:

Digital Gain Controls:

SERDES Readback Parameters:

After the wizard parameters are configured as desired, hitting “Apply” runs the startup routine for the part and configures the evaluation board. Clicking the “Read SERDES Status” button on the board diagram reads back the link status registers for CGS, Frame Sync, Good Checksum, and ILAS per link and logical lane. The Macro Tool can be used to record the startup sequence executed by the wizard. Before hitting “Apply” click the “Record” button () in the Macro Tool editor (ensure “Record Sub-Commands” is checked) and then hit “Apply”. Once the sequence is finished running a printout of the register writes to each of the parts is displayed. This recorded macro can be saved to a file and then the Macro to Hex Converter Tool (located in Start → All Programs → Analog Devices → ACE → Tools → Macro to Hex Converter) can be used to convert the cumbersome .acemacro file into an easy-to-read text file with the simple register read/write functions.

By double-clicking on the AD917x plugin on the board diagram the software will navigate down to the AD917x chip view displaying a non-interactive block diagram view representative of the functional block diagram of the part, as shown in Figure 10. By clicking the “Proceed to Memory Map” button in the bottom right hand corner the Memory Map view will be displayed and the full register map can be viewed. Using the Functional Group menu along the left hand side displays groups of controls according to functionality for a filtered view of the SPI map controls, as shown in Figure 11.

Figure 10. AD917x Chip View

Figure 11. AD917x Memory Map View

ACE also contains the Macro Tool, which can be used to record register reads and writes. This is executed in the memory map view or with the initialization wizard. To use, check the “Record Sub-Commands” checkbox and press the record button. Changes in the memory map, which are bolded until they are applied to the part, are recorded as UI commands by the macro tool once the changes are made. Changed register write commands for the controls are also recorded. Hit “Apply Changes” to execute the commands and make changes in the memory map. To stop recording, click the “Stop Recording” button. A macro tool page with the command steps will be created. The macro can be saved using the “Save Macro” button so that it may be loaded for future use.

Macro tool in ACE example view. The Stop Recording, Record, and Save Macro commands are located at the top of the macro tool.

The raw macro file will be saved using ACE syntax, which is not easily readable. To remedy this, the ACE software download includes the Macro to Hex Conversion Tool. The user can choose to include or exclude register write, reads, and/or comments in the conversion. The file pathways for the source and save paths should be the same, except that one should be an .acemacro file and the other should be a .txt file. The “Convert” button converts and opens the converted text file, which is easier to read. The conversion tool can also convert back to an .acemacro file if desired. The Macro to Hex converter tool is located in the start menu under “All Programs” --> “Analog Devices” --> “ACE” --> “Tools”.

Conversion set-up for macro to hex

Converted text file

For more information about ACE and its features, visit https://wiki.analog.com/resources/tools-software/ace.

The following steps show how to set up the AD917[2,3]-FMC-EBZ evaluation board in the conditions below:

Begin by connecting the hardware according to Figure 1 and powering up the FPGA board. Connect an SMA cable from J2 or J1 to a spectrum analyzer to measure the performance of DAC 0 or DAC1. Launch DPGDownloader from the Start Menu and add two multi-tone vectors at each of the pair of desired frequencies with the following parameters:

From the JESD Mode drop-down, select mode 1 and check the “Dual Link” checkbox. For each of the channel input drop-downs select the single-tone vector generated. All these settings should be configured as shown in Figure 12.

Figure 12. DPGDownloader Panel Setup

Figure 12. DPGDownloader Panel Setup

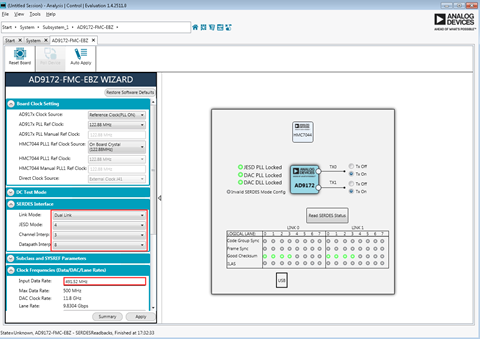

Launch ACE from the Start Menu and configure the wizard as listed below and shown in Figure 13 and Figure 14:

Figure 13. AD917x-FMC-EBZ ACE Wizard Setup

Figure 13. AD917x-FMC-EBZ ACE Wizard Setup

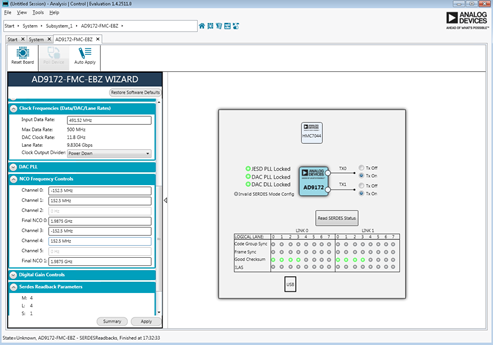

Figure 14. AD917x-FMC-EBZ ACE Wizard Setup

Figure 14. AD917x-FMC-EBZ ACE Wizard Setup

In ACE, hit “Apply” and let the sequence finish running. Then in DPGDownloader hit “Stop”, then “Download”, then “Resync”, then “Play” (should always be this order when downloading a vector or setting up the link) and the links should go high and the Serial Line Rate on the GUI should read 9.8304Gbps, as seen in Figure 15.

Figure 15. DPGDownloader Panel with Links Established

Figure 15. DPGDownloader Panel with Links Established

In ACE, hit the “Read SERDES Status” button on the board view and the readbacks should display that the JESD PLL, DAC PLL and both Logical Lane 0 and 1 on both links are high for all flag readbacks, as shown in Figure 16.

Figure 16. AD917x-FMC-EBZ ACE Setup with Links Established

Figure 16. AD917x-FMC-EBZ ACE Setup with Links Established

When looking at the spectrum, there should be tones at 1.9875GHz - 152.5MHz ± 37.5MHz = 1797.5MHz and 1872.5MHz for one band and 1.9875GHz + 152.5MHz ± 30MHz = 2110.0MHz and 2170.0MHz for the second band as shown in Figure 17.

Figure 17. AD917x-FMC-EBZ DAC0 Spectrum Output for Dual Band Case

Figure 17. AD917x-FMC-EBZ DAC0 Spectrum Output for Dual Band Case