This is an old revision of the document!

EVALUATING THE AD9121/AD9122/AD9125 DIGITAL-TO-ANALOG CONVERTER

Preface

This user guide describes both the hardware and software setup needed to acquire data capture from AD9121-M5372-EBZ/AD9121-M5375-EBZ / AD9122-M5372-EBZ/AD9122-M5375-EBZ / AD9125-M5372-EBZ/AD9125-M5375-EBZ evaluation board to characterize AD9121 14-bit / AD9122 16-bit, Dual, 1.23GSPS, TxDAC+® digital-to-analog converter or AD9125 16-bit, Dual, 1GSPS, TxDAC+® digital-to-analog converter. This guide shows how AD9121-M5375-EBZ, AD9122-M5375-EBZ, and AD9125-M5375-EBZ works with ADS7-V2/SDP-H1 controller board developed by Analog Devices. Link to the previous user guide document is provided for customers who still have the DPG2 controller board.

This guide shows how AD9121 and AD9122 Evaluation boards works with ADS7-V2/SDP-H1 controller board and how AD9125 evaluation board works with SDP-H1 controller board

Typical Setup

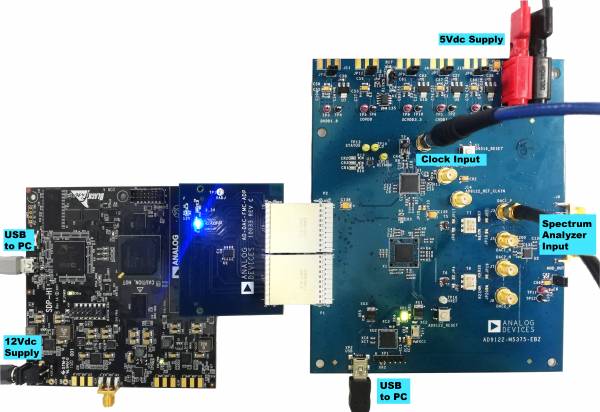

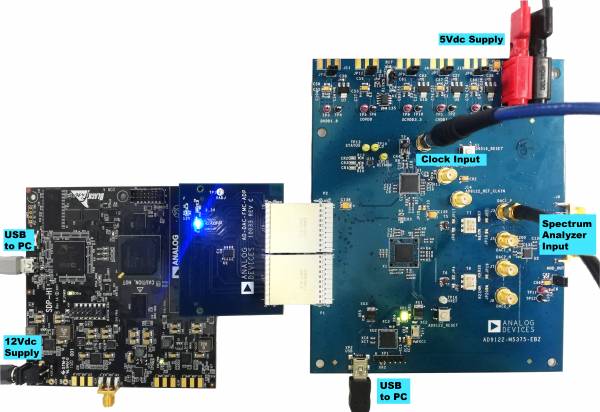

Figure 1a. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ with SDP-H1 Setup

Figure 1a. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ with SDP-H1 Setup

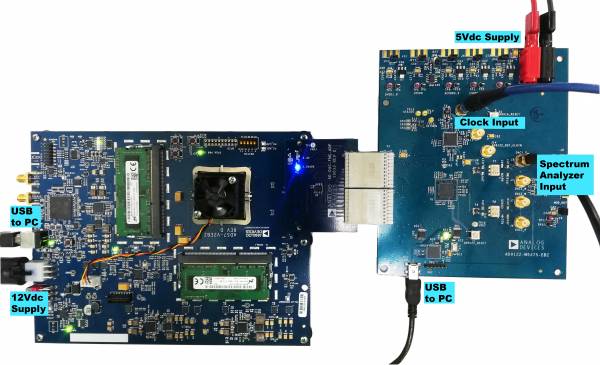

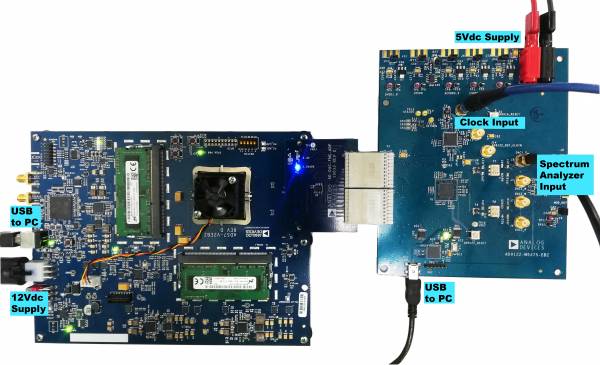

Figure 1b. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ with ADVS7-V2EBZ Setup

Figure 1b. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ with ADVS7-V2EBZ Setup

Tip: Click on any picture in this guide to open an enlarged version.

Helpful Files:

Software Needed:

Do not install ACE on a computer with DAC Software Suite.

Hardware Needed:

-

-

AD-DAC-FMC-ADP High-Speed DAC Evaluation Board to FMC Adaptor Board

PC with ACE and DPG Lite Software Applications

5Vdc Power Supply

(2) Banana Plug Cables

High-Frequency Continuous Wave Generator

Signal/Spectrum Analyzer

-

(2) SMA Cables

The following are included in SDP-H1 Evaluation Kit:

The following are included in ADS7-V2 Evaluation Kit:

12Vdc Power Supply

Power Cord

-

Quick Start Guide

Jumpers for Selecting the DAC Output

Jumpers JP4, JP5, JP6, and JP17 select the output configuration. By default, the DAC output connected to the LPF and the ADL537x analog quadrature modulator. For selecting DAC output configuration, refer to Table 1 and Figure 2.

Table 1. Jumper Configurations for Viewing DAC Output and Modulator Output

| Output Viewed | SMA Output | Jumper Configuration |

| DAC Output | J3 (DAC1_P) or J8 (DAC2_P) | JP4 and JP5 Pin 2 to Pin 3 (outer pads), JP6 and JP7 Pin 2 to Pin 3 (outer pads) |

| Modulator Output (Default) | J6 (MOD_OUT) | JP4 and JP5 Pin 1 to Pin 2 (inner pads), JP6 and JP7 Pin 1 to Pin 2 (inner pads) |

|  |

| DAC Output Configuration | Modulator Output Configuration |

Figure 2. AD9121-M5375-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ Output Configuration

Jumper for Selecting Power Supply

The evaluation board has a provision for on board or external power supply configuration.

Internal Power Supply

On board power supply is implemented by default using LDO.

JP1 selects the supply voltage level for IOVDD. Refer to Figure 3.

When Pin 1 and Pin 2 are connected, IOVDD = 3.3

V (Default)

When Pin 2 and Pin 3 are connected, IOVDD = 1.8

V

Figure 3. AD9122-M5375-EBZ IOVDD

External Power Supply

To implement external supply configuration, remove the header shunt of six pin jumpers, as shown in Figure 4. Refer to Table 2 for external supply jumper connection.

Figure 4. AD9122-M5375-EBZ Pin Jumpers

Table 2. Jumper Configurations for External Power Supply

| Supply Rail | Remove Jx Pin Jumper | Apply External Supply |

| CVDD18 | JP2 | J4 |

| DVDD18 | JP3 | J11 |

| IOVDD | JP12 | J12 |

| AVDD33 | JP8 | J13 |

| XCVDD33 | JP9 | J10 |

| AVDD5 | JP11 | TP11(+5V), TP12 (GND) |

Jumper for Selecting Clock Configuration

The AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ evaluates both the DAC outputs as well as the AQM outputs. Refer to Table 3 for clock configuration.

Table 3. Clock Configuration

| Output Viewed | Clock Input | Local Oscillator Input |

| DAC Output | J1 (CLKIN) | |

| Modulator Output (Default) | J1 (CLKIN) | J15 (LO_IN) |

The modulator LO input can be sourced through SMA connector J15 (LO_IN) with clock level at 3dBm.

Evaluation Guide

Make sure that on AD9121-M5375-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ, JP4, JP5, JP6, and JP17 are configured such that DAC output are connected with J3 (DAC1_P) or J8 (DAC2_P). Refer to Figure 2.

Follow evaluation setup in Figure 1a and 1b. AD9121/AD9122 are both compatible with ADS7/V2EBZ and SDP-H1 controller board while AD9125 is only compatible with SDP-H1 controller board.

Attach the evaluation board to SDP-H1/ADS7-V2EBZ connector using the AD-DAC-FMC-ADP adapter board.

Connect continuous wave generator for clock input to J1.

Connect the DAC output from J3 (DAC1_P) or J8 (DAC2_P) to a signal/spectrum analyzer.

Connect the evaluation board to PC via

USB and to a 5Vdc power supply via banana plug cables.

Connect SDP-H1/ADS7-V2EBZ to PC via

USB and to a 12Vdc power supply.

Set clock input/continuous wave generator to 500MHz and 2dBm.

Open ACE. The board will automatically be recognized by the software. Otherwise, install the plugin for AD9121/AD9122/AD9125 evaluation board. Double click this board then modify the configuration, as shown in Figure 5, and click “Apply”.

Figure 5. ACE Initial Configuration Wizard when using SDP-H1/ADS7-V2EBZ

Figure 5. ACE Initial Configuration Wizard when using SDP-H1/ADS7-V2EBZ

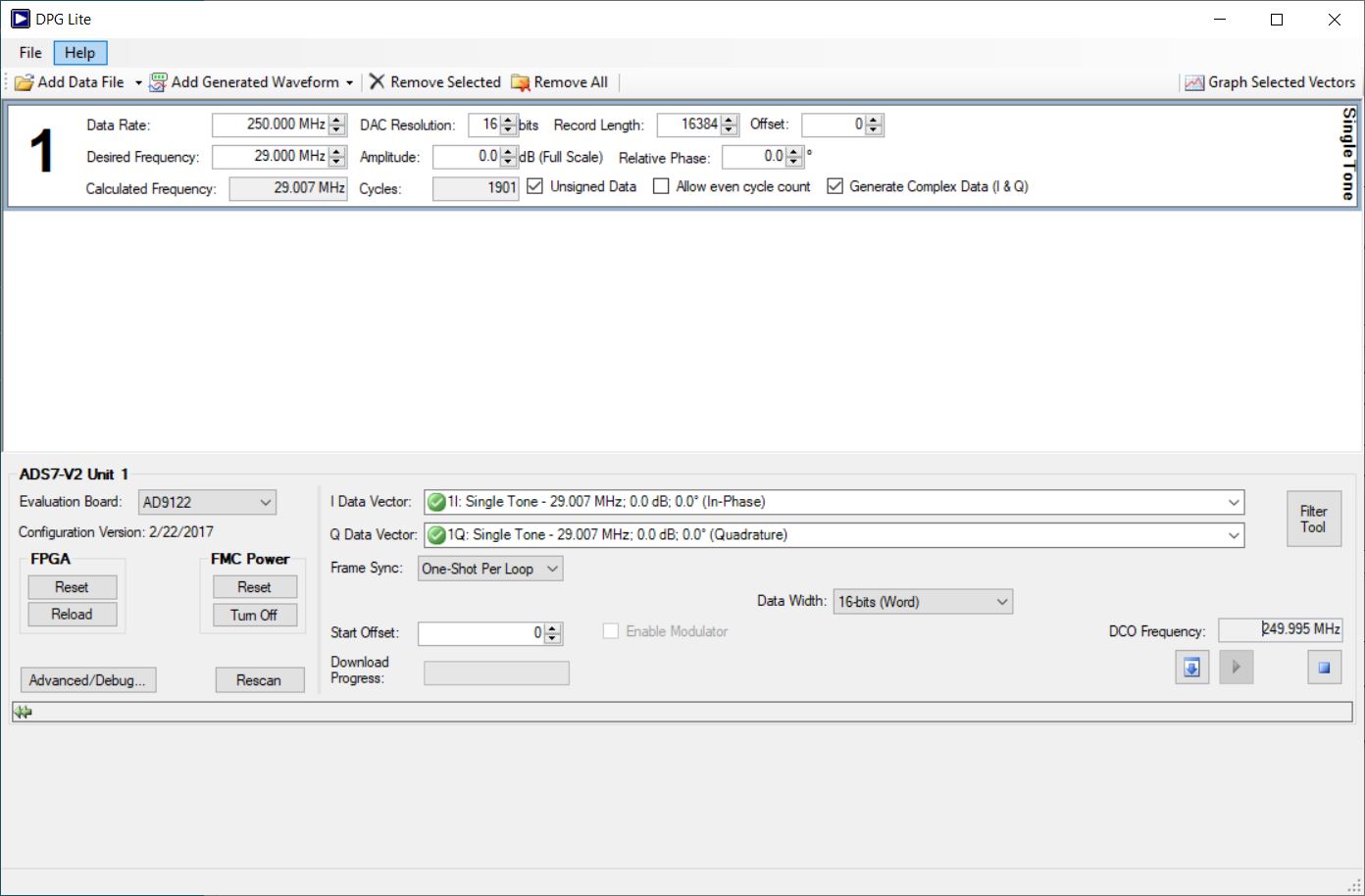

Open the DPGDownloaderLite. The evaluation board, controller board and DCO Frequency of around 250MHz will be automatically recognized by DPG.

If using AD9121 / AD9122 with SDP-H1, select LVDS as port configuration.

If using AD9125 with SDP-H1, select LVCMOS-1.8Vas port configuration.

If using AD9121 / AD9122 with

ADS7-V2EBZ, use default configuration.

Figure 6. AD9121/AD9122 SDP-H1 Port Configuration / AD9125 SDP-H1 Port Configuration

Figure 6. AD9121/AD9122 SDP-H1 Port Configuration / AD9125 SDP-H1 Port Configuration

In DPGDownloaderLite,

Add Generator Waveforms pulldown menu select Single Tone and apply the settings as shown in Figure 7. Set the

Data Rate to 250MHz and

Desired Frequency to 29

MHz. Set

DAC Resolution to the DAC’s number of bits to:

14 bits for AD9121;

16 bits for AD9122/AD9125. Check the “Generate Complex Data (I & Q)” box and “Unsigned Data” box.

Select the in-phase tone from the

I Data Vector pulldown menu and the quadrature tone from the

Q Data Vector pulldown menu.

Figure 7. DPGDownloader Waveform Configuration for AD9122-M5375-EBZ

Figure 7. DPGDownloader Waveform Configuration for AD9122-M5375-EBZ

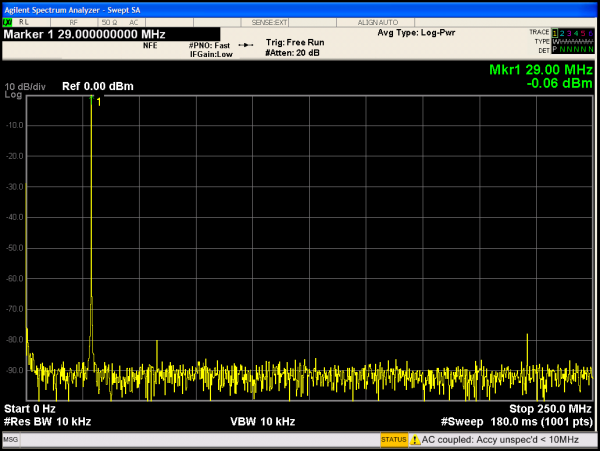

Press the download arrow and then the play button. The spectrum similar to Figure 8 should appear in the signal/spectrum analyzer.

Figure 8. AD9122-M5375-EBZ FFT for Fdac=500MHz,2x Interpolation Fout=29MHz

Figure 8. AD9122-M5375-EBZ FFT for Fdac=500MHz,2x Interpolation Fout=29MHz

This version (22 Jun 2022 03:08) was approved by Deferson Romero.The Previously approved version (09 May 2018 17:22) is available.

This version (22 Jun 2022 03:08) was approved by Deferson Romero.The Previously approved version (09 May 2018 17:22) is available.

Figure 1a. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ with SDP-H1 Setup

Figure 1a. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ/AD9125-M5375-EBZ with SDP-H1 Setup

Figure 1b. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ with ADVS7-V2EBZ Setup

Figure 1b. AD9121-M5372-EBZ/AD9121-M5375-EBZ/AD9122-M5372-EBZ/AD9122-M5375-EBZ with ADVS7-V2EBZ Setup