This document presents the steps to setup an environment for using the EVAL-CN0216-SDPZ evaluation board together with the Xilinx KC705 FPGA board and the Xilinx Embedded Development Kit (EDK). Below is presented a picture of the EVAL-CN0216-SDPZ Evaluation Board with the Xilinx KC705 board.

For component evaluation and performance purposes, as opposed to quick prototyping, the user is directed to use the part evaluation setup. This consists of:

The SDP-B controller board is part of Analog Devices System Demonstration Platform (SDP). It provides a high speed USB 2.0 connection from the PC to the component evaluation board. The PC runs the evaluation software. Each evaluation board, which is an SDP compatible daughter board, includes the necessary installation file required for performance testing.

Note: it is expected that the analog performance on the two platforms may differ.

Below is presented a picture of SDP-B Controller Board with the EVAL-CN0216-SDPZ Evaluation Board.

The EVAL-CN0216-SDPZ board is a precision weigh scale signal conditioning system. It uses the AD7791, a low power buffered 24-bit sigma-delta ADC along with two external ADA4528-1 zero-drift amplifiers. This solution allows for high dc gain with a single supply.

The AD7791 is a low power, complete analog front end for low frequency measurement applications. It contains a low noise 24-bit S-? ADC with one differential input that can be buffered or unbuffered.

The device operates from an internal clock. Therefore, the user does not have to supply a clock source to the device. The output data rate from the part is software programmable and can be varied from 9.5 Hz to 120 Hz, with the rms noise equal to 1.1 µV at the lower update rate. The internal clock frequency can be divided by a factor of 2, 4, or 8, which leads to a reduction in the current consumption. The update rate, cutoff frequency, and settling time will scale with the clock frequency.

The first objective is to ensure that you have all of the items needed and to install the software tools so that you are ready to create and run the evaluation project.

Before connecting the ADI evaluation board to the Xilinx KC705 make sure that the VADJ_FPGA voltage of the KC705 is set to 3.3V. For more details on how to change the setting for VADJ_FPGA visit the Xilinx KC705 product page.

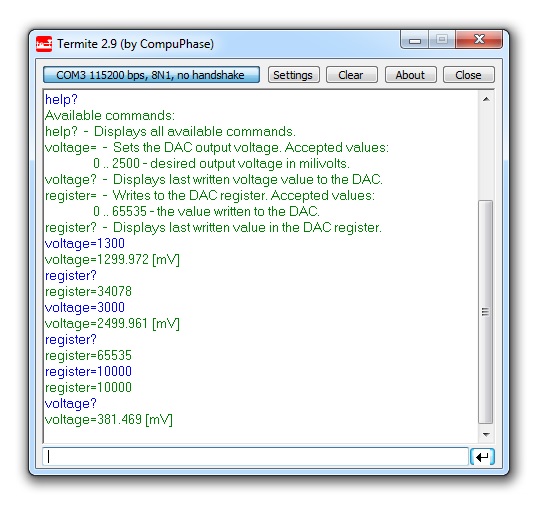

The following commands were implemented in this version of EVAL-CN0216 reference project for Xilinx KC705 FPGA board.

| Command | Description |

|---|---|

| help? | Displays all available commands. |

| adcCode? | Displays the ADC Code. |

| ad7791Reset! | Resets the serial interface with the AD7791. |

Commands can be executed using a serial terminal connected to the UART peripheral of Xilinx KC705 FPGA.

The following image shows a generic list of commands in a serial terminal connected to Xilinx KC705 FPGA's UART peripheral.

The hardware platform for each reference projects with FMC-SDP interposer and KC705 evaluation board is common. The next steps should be followed to recreate the software project of the reference design: