This is an old revision of the document!

AD-FMCOMMS1-EBZ HDL Reference Design

Supported Devices

Supported Carriers

Download

FPGA Reference Designs on GitHub :

Generating Xilinx netlist files

The repository will not contain Xilinx netlist files. If you need to build the design, you must generate these files. The following steps illustrate the process using coregen.

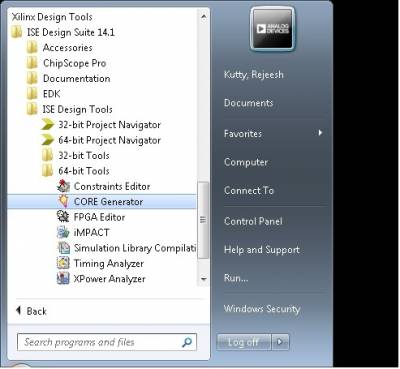

| Open coregen, the default path is “Xilinx Design Tools → ISE Design Suite 14.1 → ISE Design Tools → 64-bit Tools → CORE Generator” |  |

| If you have an existing project file, use that. Otherwise click “File→New Project” |  |

| Pick a directory location in this case it is “C:/fpgahdl_xilinx” |  |

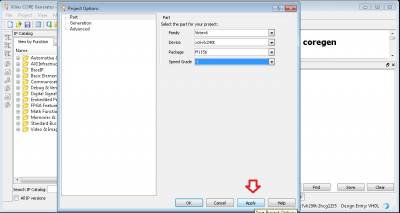

| Under the “Part” tab, select family: “Virtex6”, Device: “xc6vlx240t”, package: “ff1156” and Speed Grade: “-1”. This corresponds to ML605. You may use this same selection, even if you are targeting a KC705 or ZC702 board. Click on “Apply”. |  |

| Under the “Generation” tab, select Design Entry: “Verilog”. Click on “OK”. |  |

| Now we need the list of modules to generate the netlist files. The repository contains xco files for each of the netlist file that is missing. A windows search for “*.xco” or “find” should give us the list. find cf_lib/edk/pcores -name “*.xco” |  |

| In coregen, select “Project → Import Existing Customized IP”, and add all the xco files. |  |

| Change the view (left bottom) to “Project IP”, make sure all the xco files are imported. |  |

| Select “Project → Regenerate all project IP (under current project settings)”. This could take a while especially for the FFT core. |  |

| Once complete, copy the “*.ngc” files to the respective “netlist” and “*.v” files to the respective “hdl/verilog” directories. You may now open XPS and rebuild the project. |  |

Tar file contents

The tar file contains, in most cases, the following files and/or directories. To rebuild the reference design simply double click the XMP file and run the tool. Please refer to Xilinx EDK documentation for details.

| license.txt | ADI license & copyright information. |

| system.mhs | MHS file. |

| system.xmp | XMP file (use this file to build the reference design). |

| data/ | UCF file and/or DDR MIG project files. |

| docs/ | Documentation files (Please note that this wiki page is the documentation for the reference design). |

| sw/ | Software (Xilinx SDK) & bit file(s). |

| cf_lib/edk/pcores | pcores (if used). |

This version (02 Aug 2013 18:10) was approved by Lars-Peter Clausen.The Previously approved version (04 Apr 2013 18:19) is available.

This version (02 Aug 2013 18:10) was approved by Lars-Peter Clausen.The Previously approved version (04 Apr 2013 18:19) is available.